Altium Designer の新機能

このページでは、Altium Designer 24 の初期バージョンに含まれる改善点と、その後の更新で追加した改善点について説明します。様々な改善を提供することに加えて、各更新には、AltiumLive コミュニティの BugCrunch システムを通じてお客様から寄せられたフィードバックに基づいて、ソフトウェア全体に多数の修正と拡張機能を導入し、設計者が最先端の電子技術を作成し続けるのに役立ちます。

Altium Designer 24.3

リリース日: 2024年3月19日 – バージョン 24.3.1 (build 35)

Altium Designer 24.3.1 のリリースノート

PCB デザインの改善

絶対値としてのパッドコーナー半径/面取り (Open Beta)

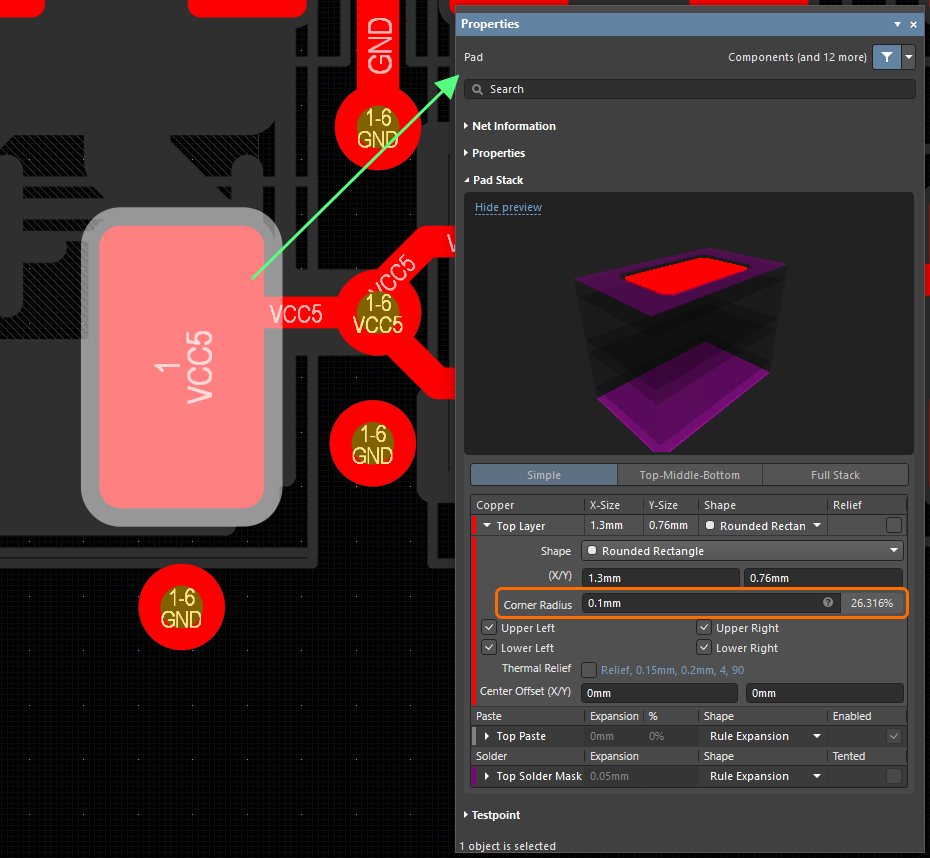

このバージョンでは、パッドのコーナー半径/面取りを絶対値 (mil、または mm) として定義する機能を追加しました。

Rounded Rectangle、または Chamfered Rectangle 形状のパッド (銅箔、paste、または solder layer 上)が PCB、または PCB フットプリント エディタで選択されている時、Corner Radius 欄へ値を入力して半径/面取りを絶対値として定義できます ( デフォルトの測定単位を使用)。パッドのコーナー半径/面取りの絶対値は、パッドの最短辺の半分以下でなければならないことに注意してください。計算された割合値がその欄の右側に表示されます。

Corner Radius 欄へ値を入力して、絶対値として定義できます。

値の後に % 記号を入力して、パッドの最短辺の半分の割合として半径/面取りを定義できます (以前のバージョンと同様)。

パッドコーナー半径の面取りの絶対値は、PCB List と PCBLIB List パネル、Find Similar Objects ダイアログ、および Pad/Via Template エディタ でも対応しています。また、以下のクエリキーワードを式で使用できるようになりました:

| キーワード | 概要 |

|---|---|

|

|

クエリに準拠するレイヤの Pad Corner Radius Size プロパティのパッドオブジェクトが示されます。 例えば、 |

|

|

クエリに準拠するレイヤの Pad Corner Radius Uses Percent プロパティのパッドオブジェクトが示されます。 例えば、 |

Xpedition デザインをインポートする 時、絶対値として定義されたパッドのコーナー半径/面取りも インポート ウィザード で対応しました。

PCB 複製の改善

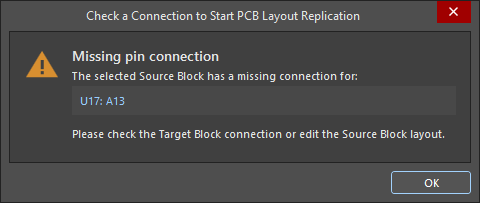

強化したエラー通知

Layout Replication ツールを実行時に、選択したソースブロックで欠落しているピン接続が検出された場合、警告ダイアログが表示され、欠落している接続について通知されます。

ダイアログ内のリンクをクリックして、問題のあるオブジェクトをクロスプローブできます。

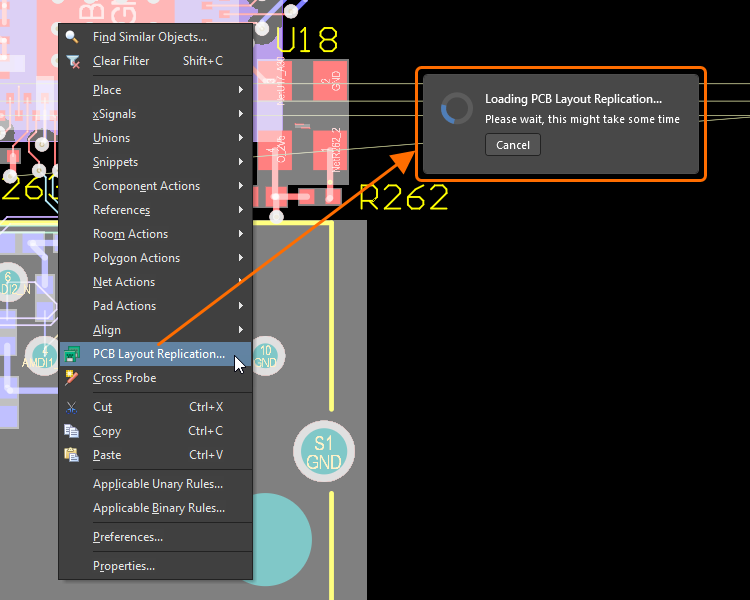

PCB 複製に 'Busy' 状態を追加

PCB 複製プロセスにより応答性の高い UI を提供するために、この機能の 'busy' 状態のインジケーターをこのバージョンで追加しました。

-

Layout Replication ツールを実行した時、PCB Layout Replication ダイアログを開く前に、複製データが読み込み中であることを示すメッセージが表示され、必要に応じて、プロセスをキャンセルできます。

- PCB Layout Replication ダイアログの Replicate ボタンをクリックした後、最初のブロックが配置される (または、インタラクティブモードで配置の準備ができる) 前に、カーソルが 'in progress' (

) と表示されます。

) と表示されます。

制約マネージャの改善

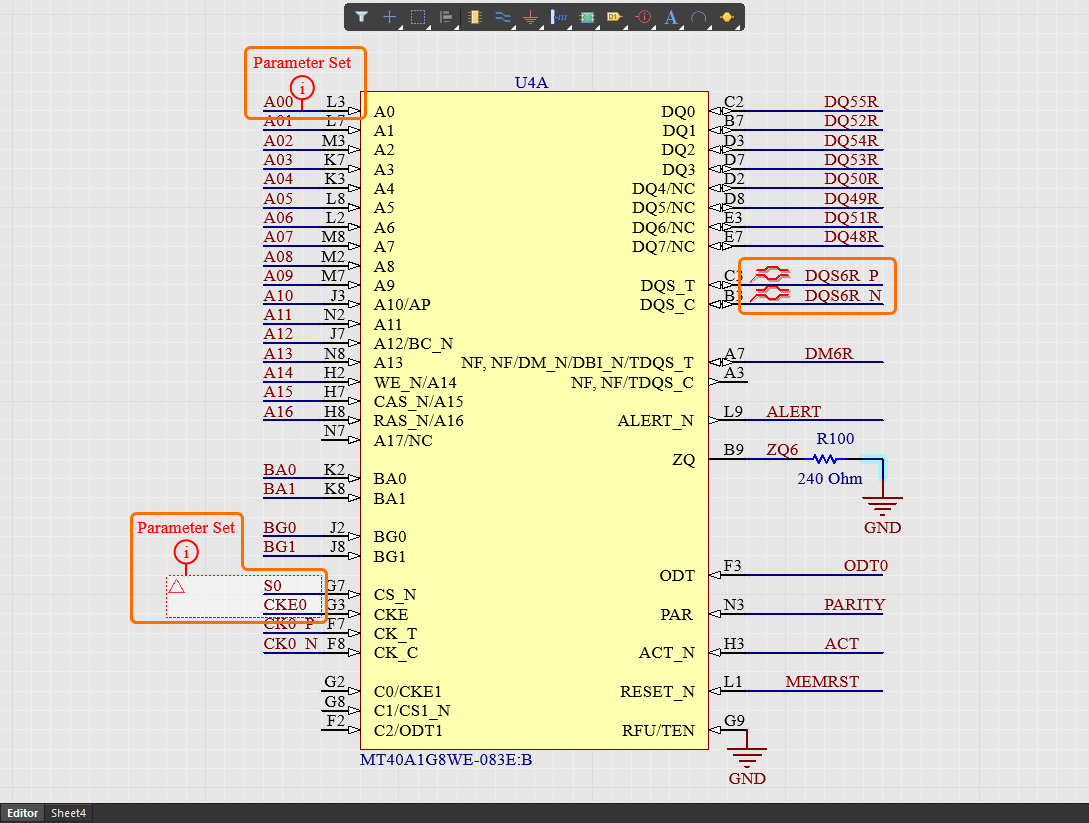

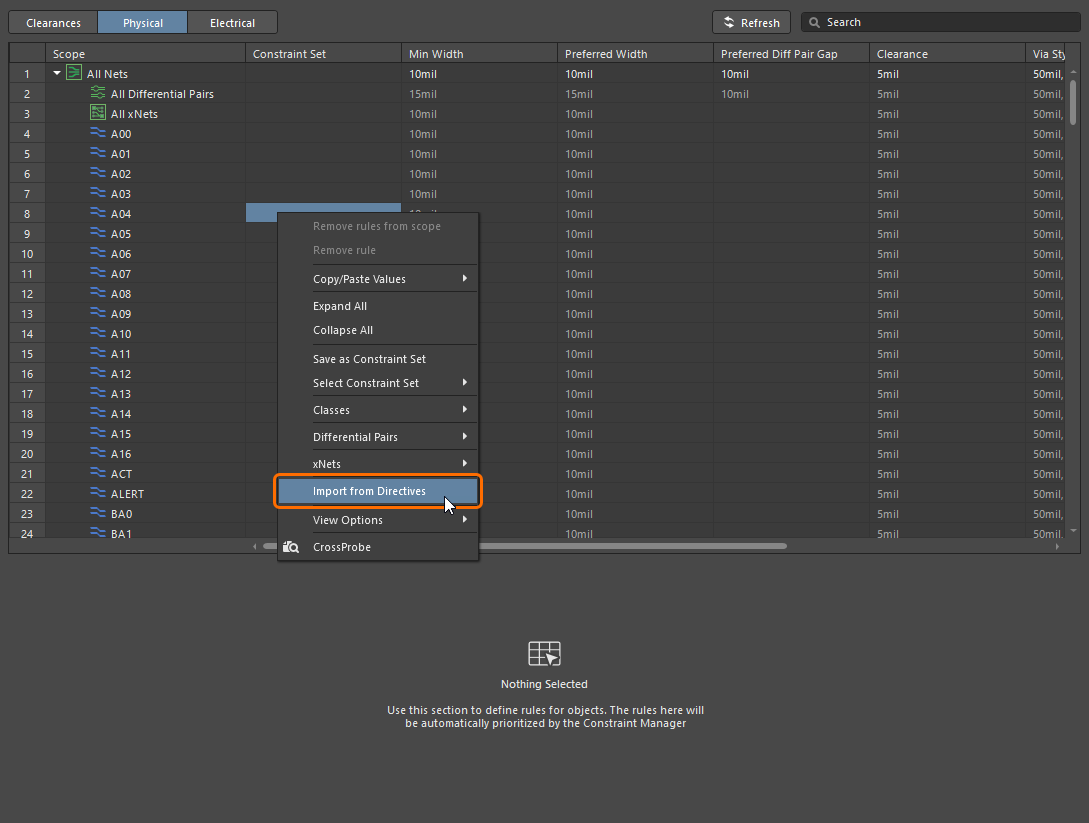

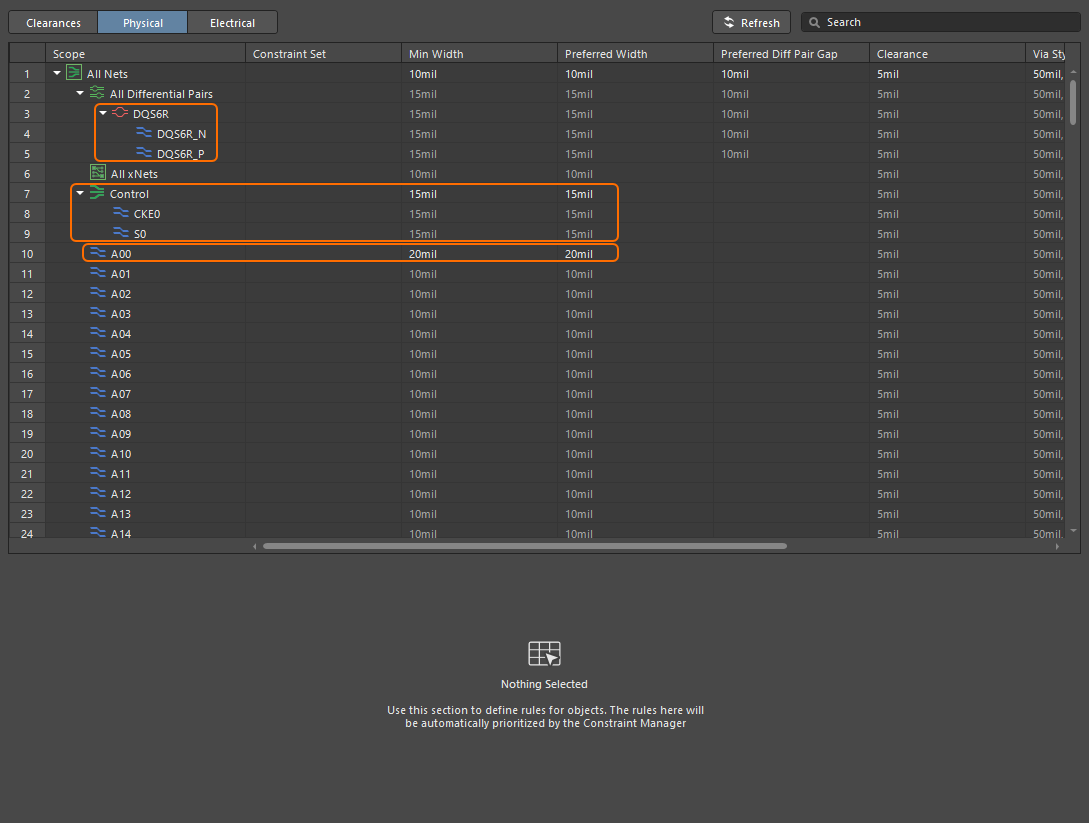

デザイン ディレクティブのインポートの対応 (Open Beta)

回路図ソース ドキュメントに配置、および定義されたデザイン ディレクティブの制約を C制約マネージャ へインポートできるようになりました。これは、新しい Import from Directives コマンド (右クリックメニューから) を使用して、Physical、または Electrical ビュー (回路図から 制約マネージャ にアクセスする時) から実行され、ルール、ネットクラス、差動ペア、および差動ペアクラス ディレクティブを対応します。

| ❯❮

回路図上には、いくつかのパラメータセット、および差動ペア ディレクティブが配置されています。これらのディレクティブは、差動ペア、ネットクラス、Width ルールを定義します。

制約マネージャ で右クリックメニューから Import from Directives コマンドを使用。

ディレクティブのデータは 制約マネージャ へインポートされます。 |

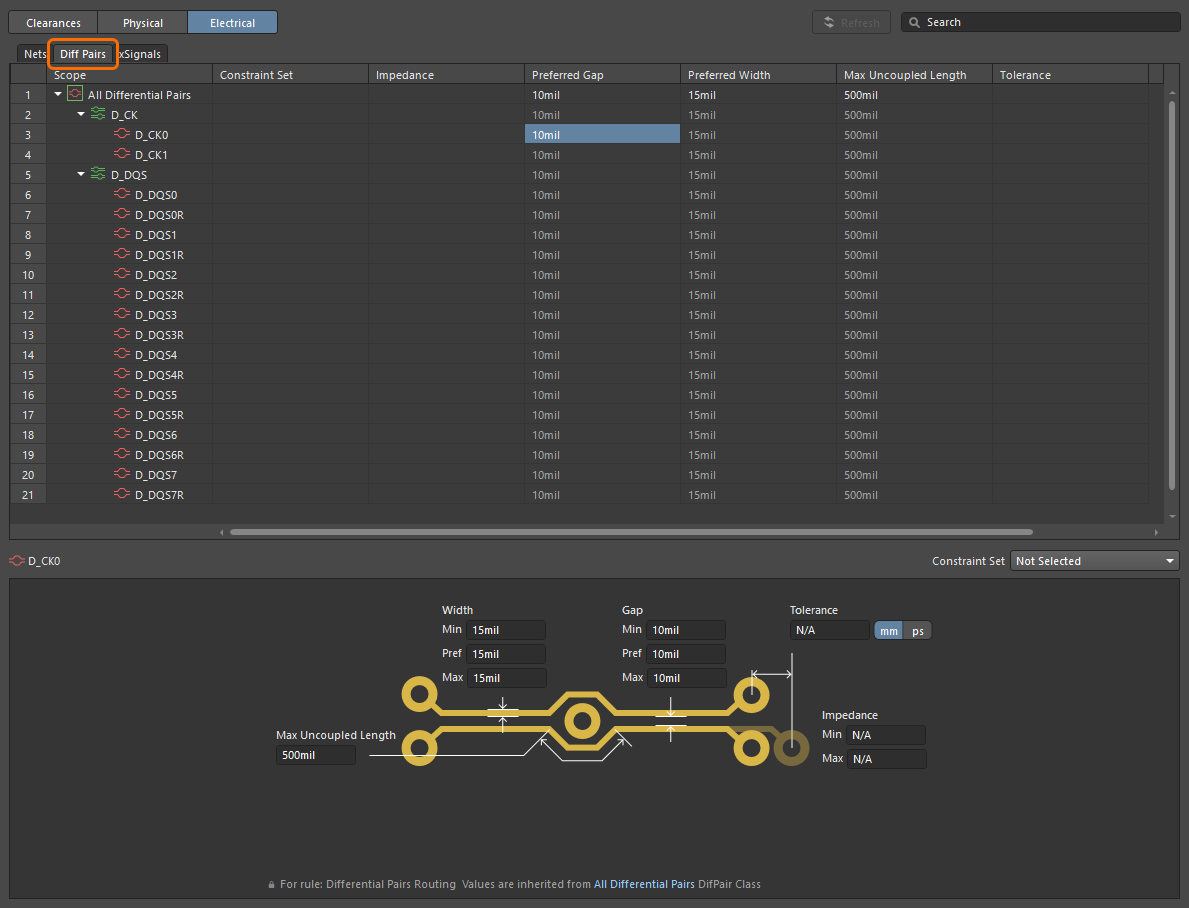

新しい 'Diff Pairs' タブ

新しい Diff Pairs タブが、差動ペアを明確に定義、および管理するための Electrical constraints ビューから利用できるようになりました。このタブには、デザインの差動ペアの階層リストが表示されます。差動ペア、または差動ペアクラスのセルを選択して、制約マネージャ の下部領域にその制約を表示できます。

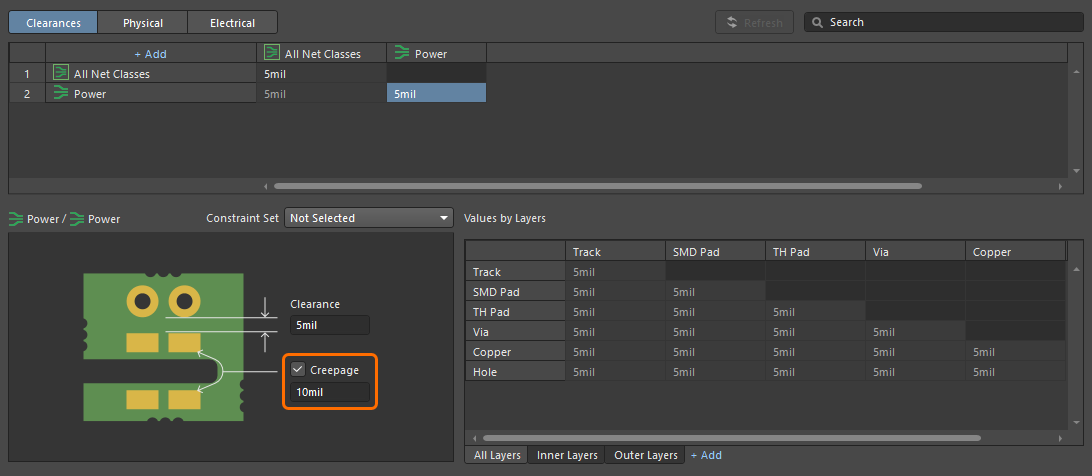

クリアランス マトリクスでの沿面距離の対応

Clearances ビューのマトリクスを使用して、ネットと/または差動ペアのクラス間の電気的クリアランスを定義する時、Creepage ルールを指定できるようになりました。

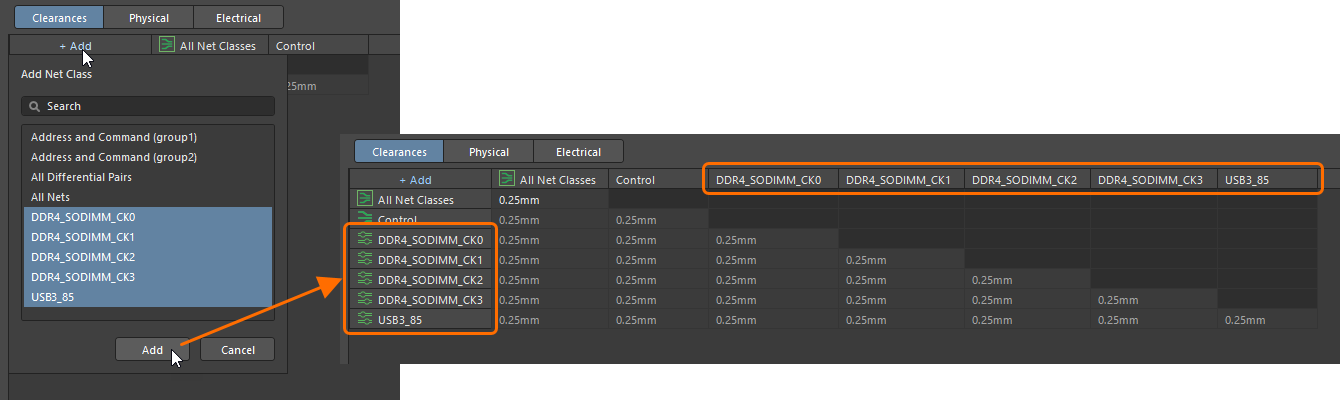

クリアランス マトリクスでのマルチ編集の対応

選択した行/列内でのマルチ編集のためのクリアランス マトリクス (Clearance ビュー) を対応しました。制約マネージャ の詳細なクリアランス設定で、行、または列を選択し、必要な値を入力し、Enter キーを押すかクリックして、この値を行/列の全てのセルへ適用できます。

Draftsman の改善

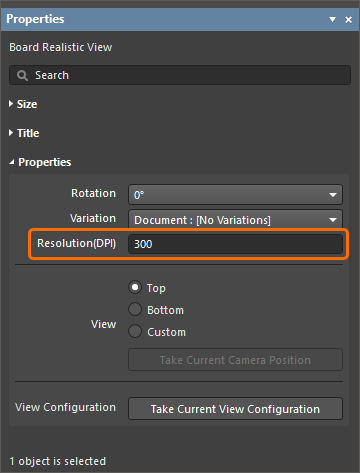

Board Realistic View の解像度を変更する機能

配置された Board Realistic View の解像度は、Properties パネルの Properties 領域にある Resolution(DPI) 欄に目的の解像度を入力することで設定できるようになりました。以前は、ビューは静的なレンダリング画像であり、解像度を変更する方法はありませんでした。最小設定は 75 DPI、デフォルト設定は 300 DPI です。

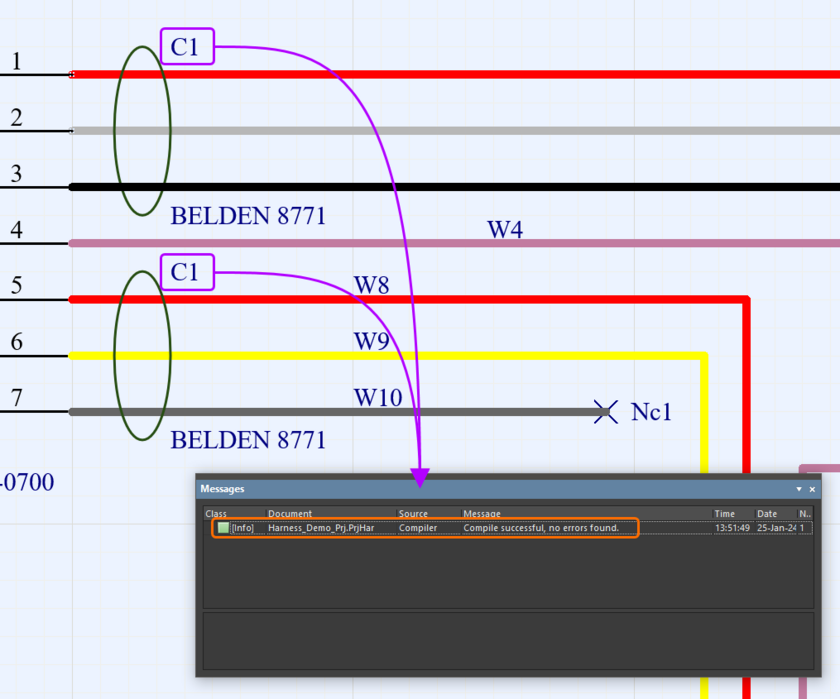

ハーネスデザインの改善

Cavity の強化

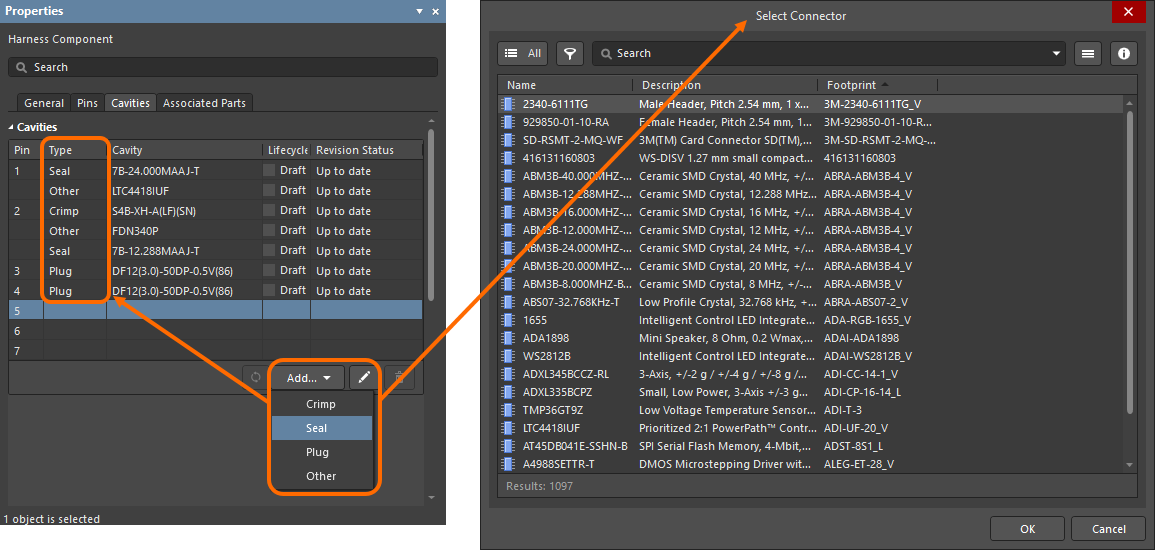

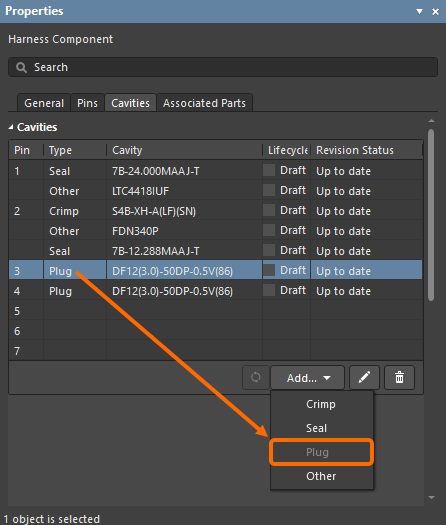

Cavity タイプの指定

Wiring Diagram (*.WirDoc) でハーネスコンポーネントの各ピンの cavity のタイプを指定できるようになりました。Properties パネルの Cavities タブで、目的のピンを選択し、Add をクリックします。ドロップダウンから cavity タイプを選択します。表示される Select Connector ダイアログで、ピンのための目的のコネクタを選択します。

特定のタイプの cavity は 1 つだけピンへ追加できます。特定のタイプの cavity が追加されると、下図の Pin 3 に示すように、ドロップダウンでそのエントリは使用できなくなります (グレー表示されます)。

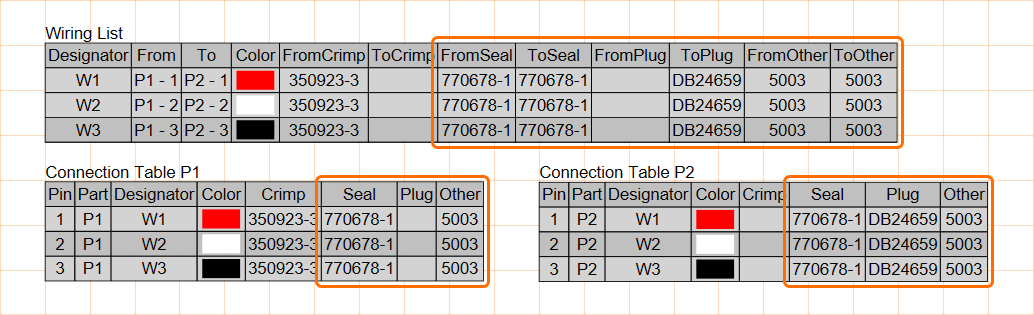

Wiring List と Connection Table へ新しい Cavity タイプを追加

Seal、plug、その他の cavity 部品を製造図の wiring list と connection table に表示できます。配置された表がデザインスペースで選択されている時、Properties パネルの Columns タブで目的の列の表示を有効にします。

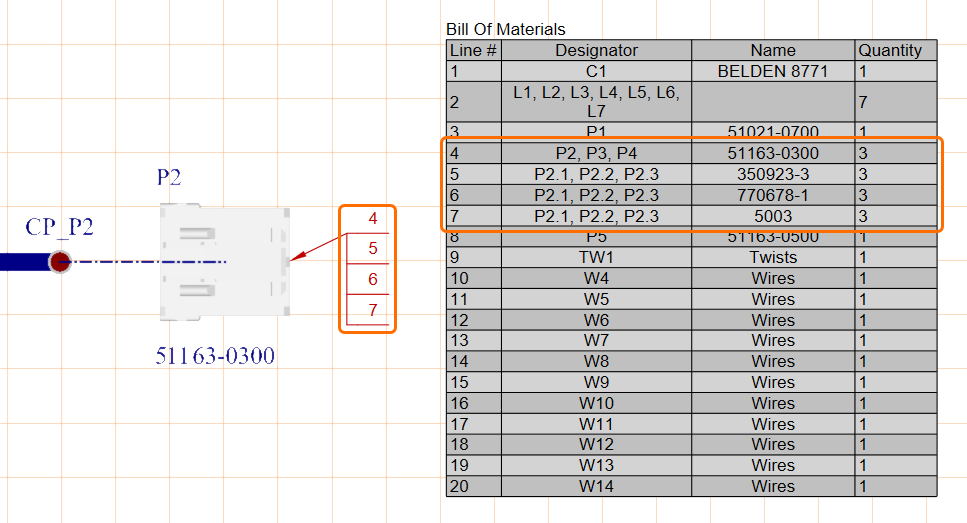

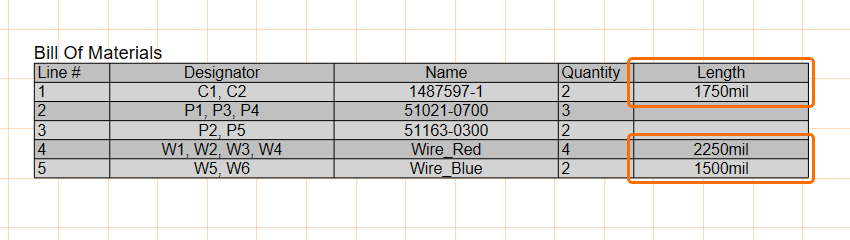

Cavity BOM Line Numbers を製造図のコールアウトへ追加

BOM Item を表示するコールアウトセットが layout drawing ビュー上のコンポーネントの物理ビューへ追加されると、割り当てられた全ての cavity の BOM line numbers が含まれます。

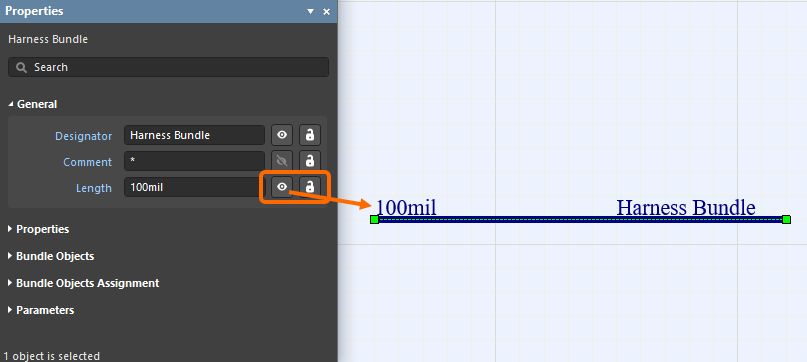

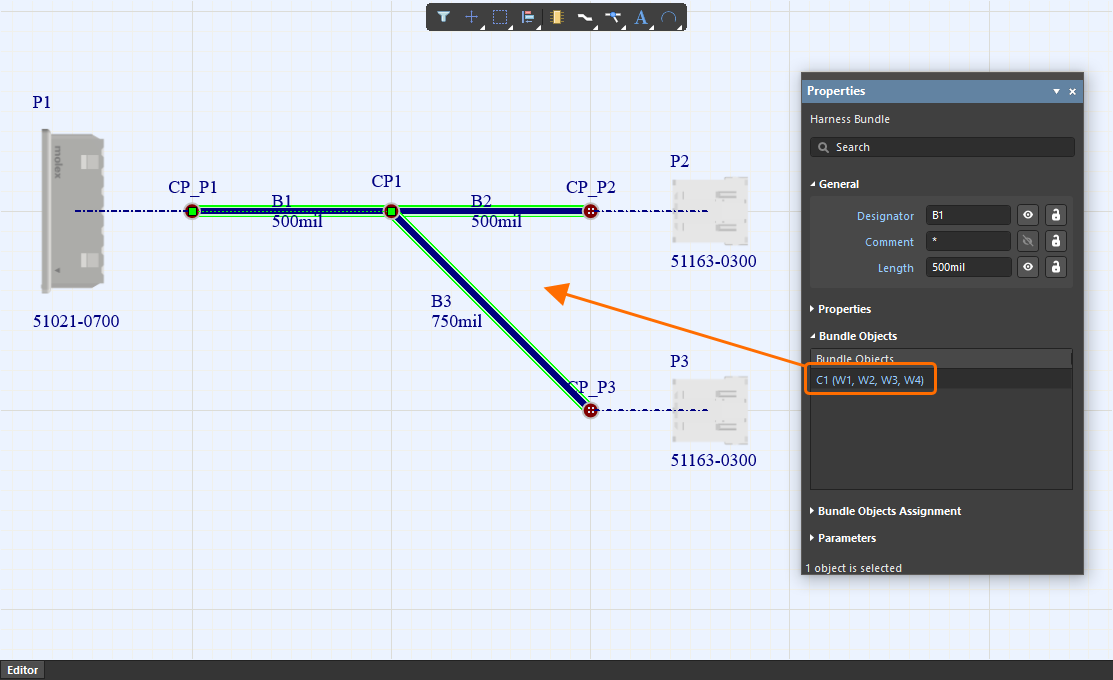

ハーネスバンドルの Length パラメータの表示設定とロック オプション

Layout Drawing (*.LdrDoc) のハーネスバンドルの Length パラメータに、表示とロック オプションが含まれるようになりました。

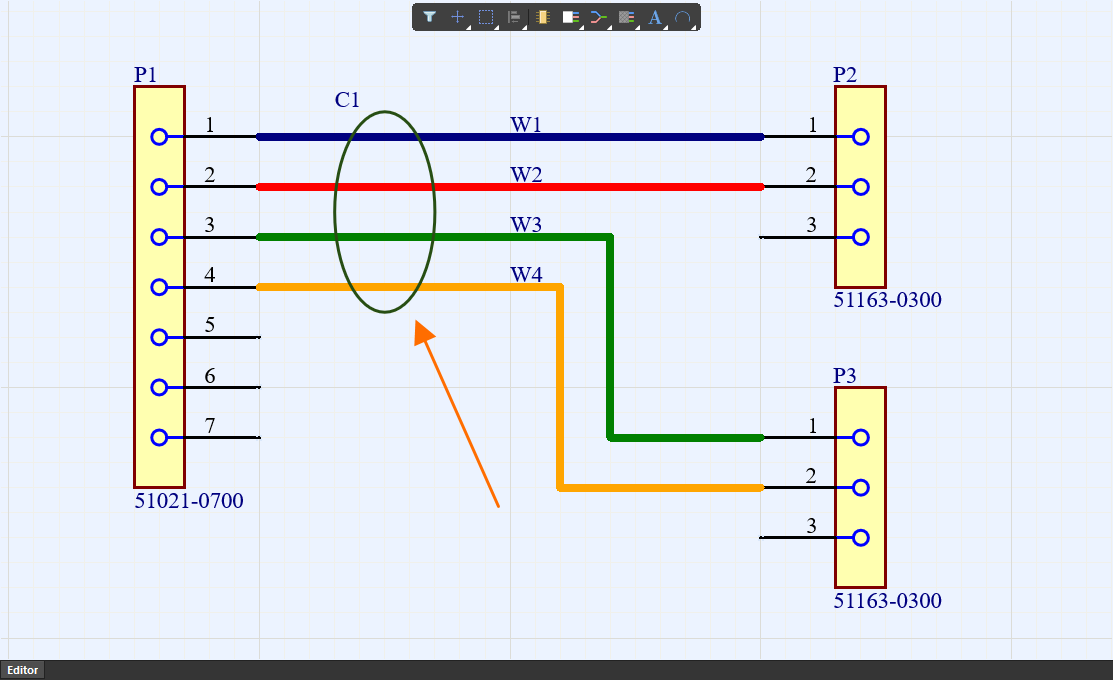

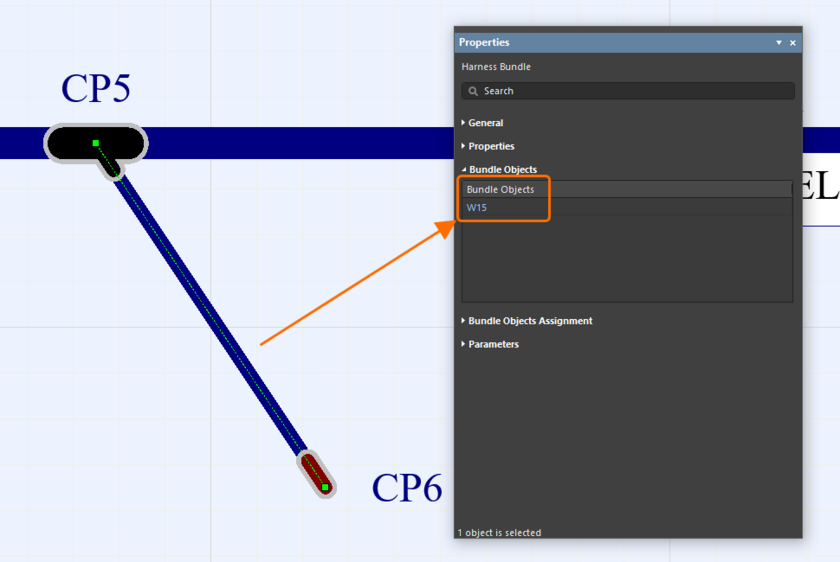

分割ケーブルのワイヤを含むバンドルをハイライト表示

Properties パネルの Bundle Objects 領域でケーブルを選択すると、分割ハーネスケーブルのワイヤを含む全てのハーネスバンドルが Layout Drawing (レイアウト図) 上でハイライト表示されるようになりました。分割ケーブルの場合、最長のワイヤの長さが BOM に表示されます。

| ❯❮

ケーブル

選択したバンドルの Properties パネルの Bundle Objects 領域で cable エントリをクリックすると、

BOM では、最長のワイヤ (この例ではバンドル |

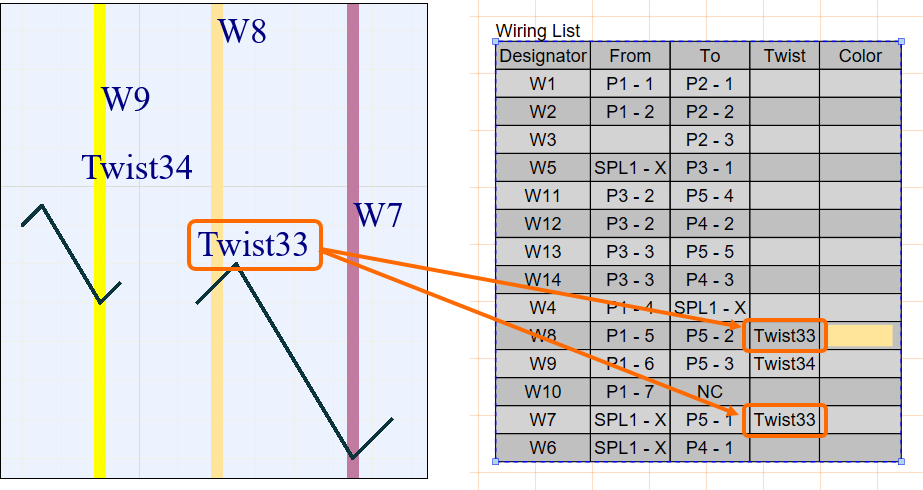

ツイスト オブジェクトのデジグネータを Wiring List へ追加

下図に示すように、ツイスト オブジェクトのデジグネータが wiring list に表示されるようになりました。

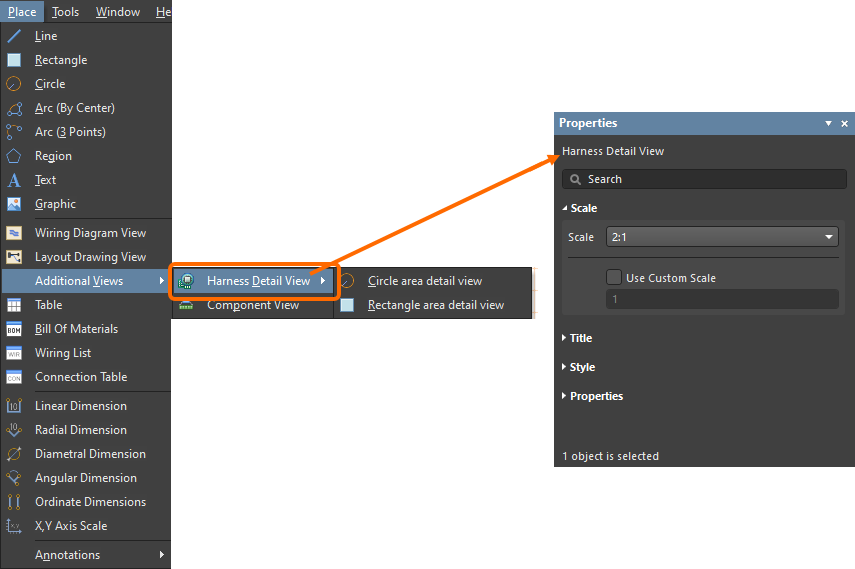

Board Detail View の名称を Harness Detail View に変更

Harness Draftsman ドキュメント (*.HarDwf) の Board Detail View の名称を Harness Detail View に変更しました。

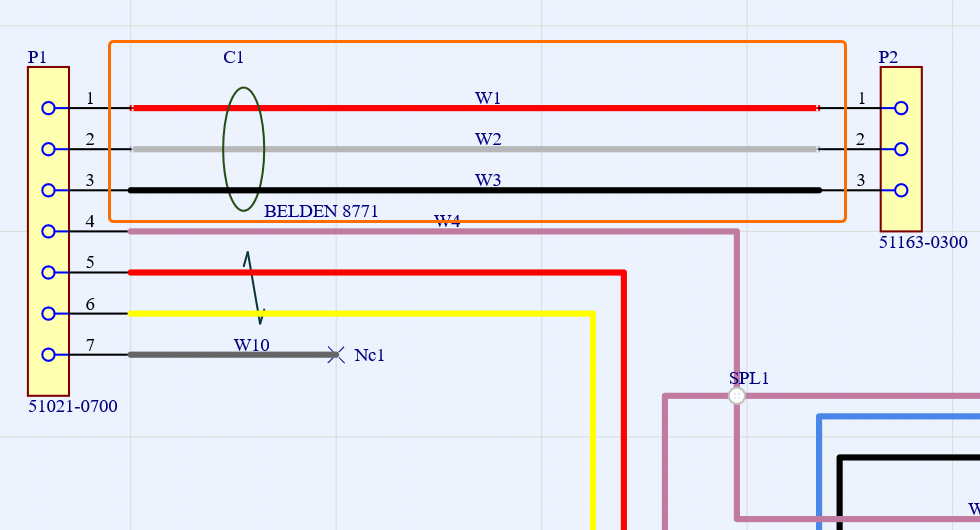

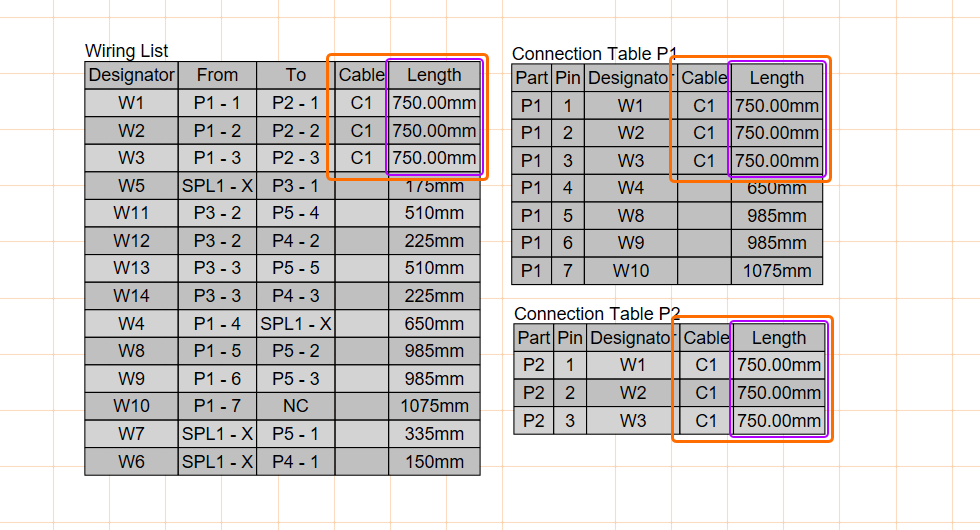

Wiring List と Connection Tableで個々のワイヤ長を表示

wiring list と connection table の Length 列に、ケーブル内の各ワイヤの個別のワイヤ長が表示されるようになりました。

| ❯❮

ワイヤ

これらのワイヤの個々の長さが wiring list と connection table に表示されるようになりました。 |

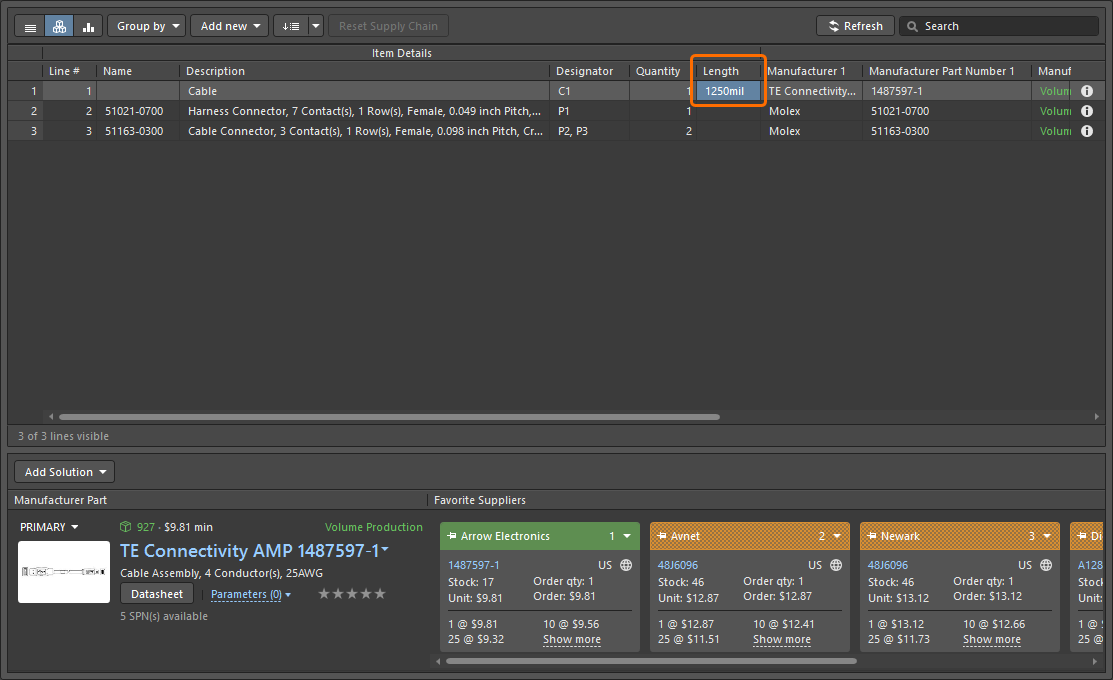

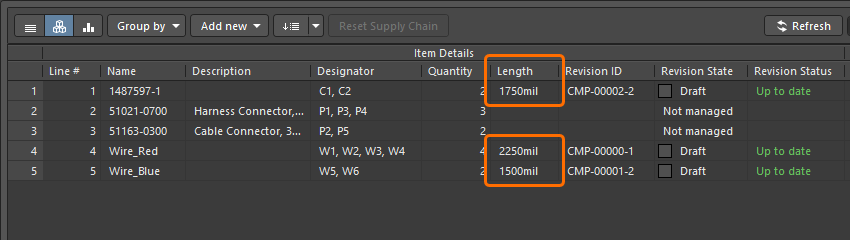

BOM にワイヤとケーブルの全長を表示

harness wiring コンポーネント の場合、ActiveBOM ドキュメント、および製造図の BOM Table の Length 列には、同じ BOM item のワイヤ/ケーブルの個々の長さではなく、合計の長さが表示されるようになりました。

データ管理の改善

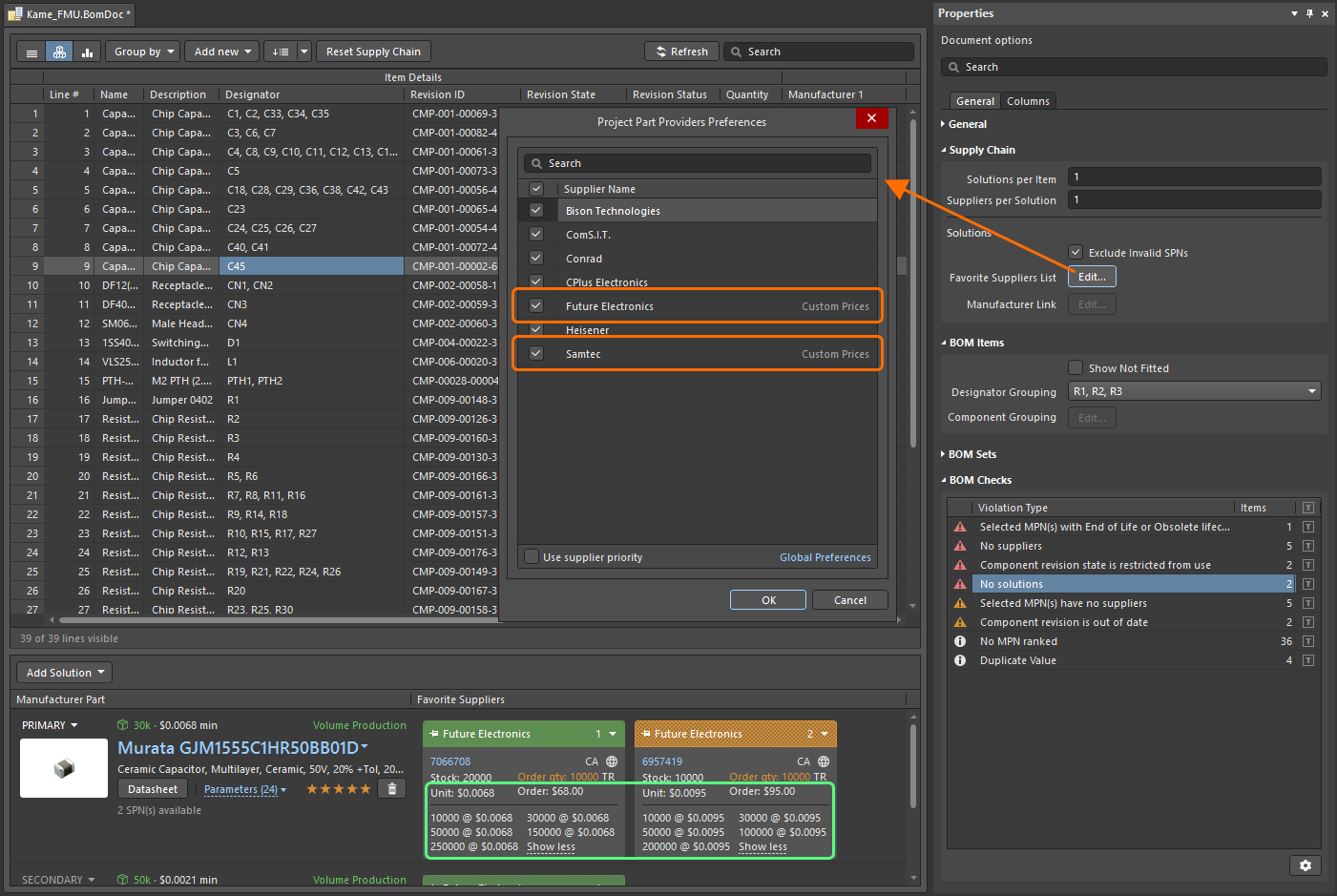

カスタム価格の対応

Altium 365 Workspace のブラウザ インターフェースを介して特定のサプライヤー アカウントへの接続を設定した時 (詳細を見る)、ActiveBOM、および part choices にアクセスする全ての場所で、該当するカスタム価格を確認できるようになりました。また、カスタム価格を提供するサプライヤーには、Project Part Providers Preferences ダイアログでそのようにラベルが付けられます。このダイアログには、ActiveBOM ドキュメントの Properties パネルの Favorite Suppliers List 欄の Edit ボタンをクリックしてアクセスできます。

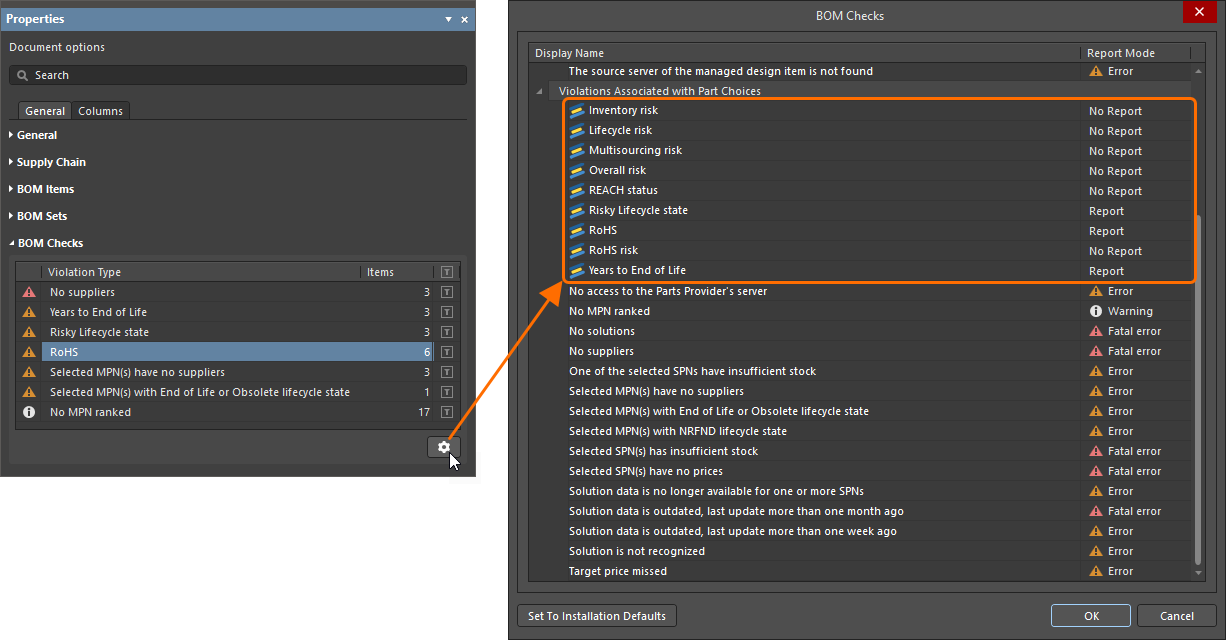

SiliconExpert パラメータの BOM チェックを追加

SiliconExpert パラメータに基づく一連のチェックを ActiveBOM で対応しました。これらのチェックは、BOM Checks ダイアログの Violations Associated with Part Choices カテゴリで有効、または無効にできます。Properties パネルの BOM Checks 領域にある ![]() ボタンをクリックして、ダイアログを開きます。

ボタンをクリックして、ダイアログを開きます。

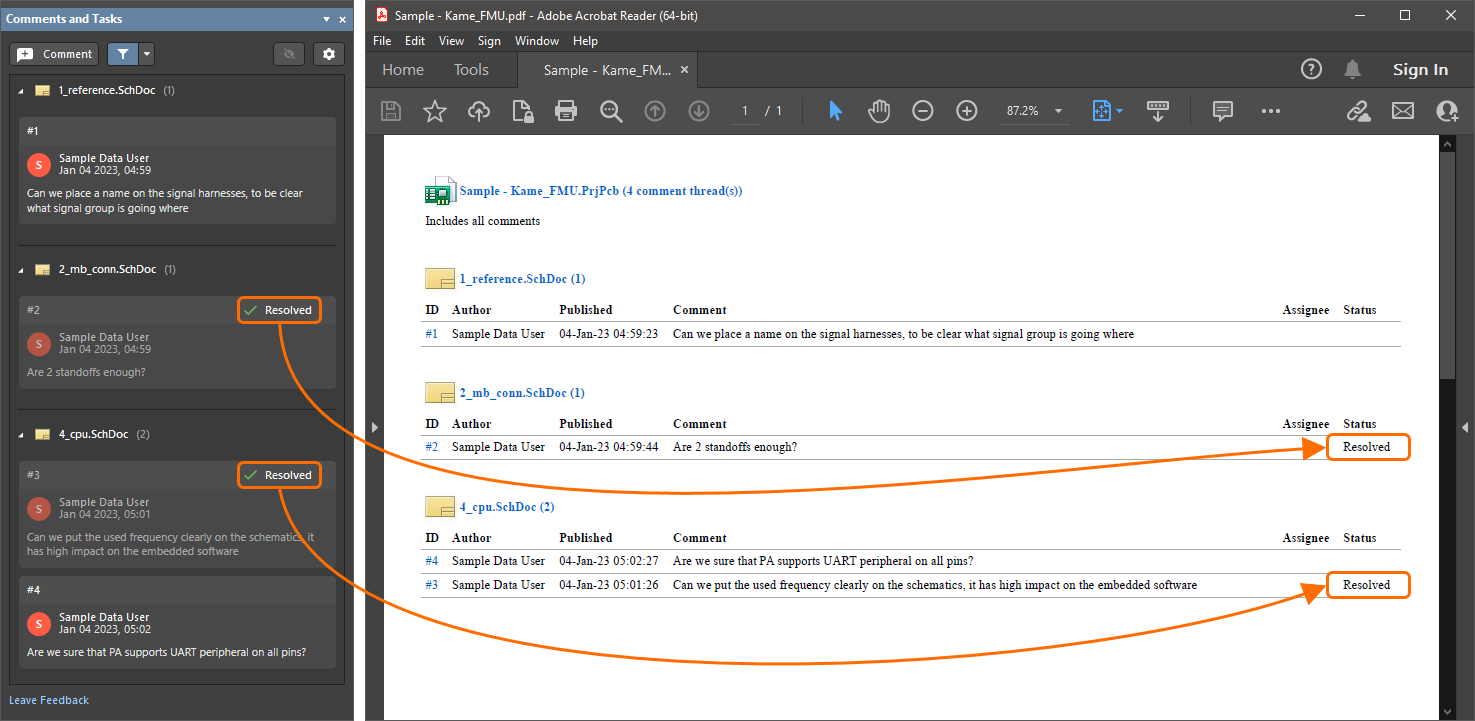

エクスポートされた PDF へコメントの Resolved Status を追加

コメントを PDF へエクスポートした時、解決された簡単なコメント (つまり、'tasks' として割り当てられていないコメント) のステータスがエクスポートに含まれるようになりました。

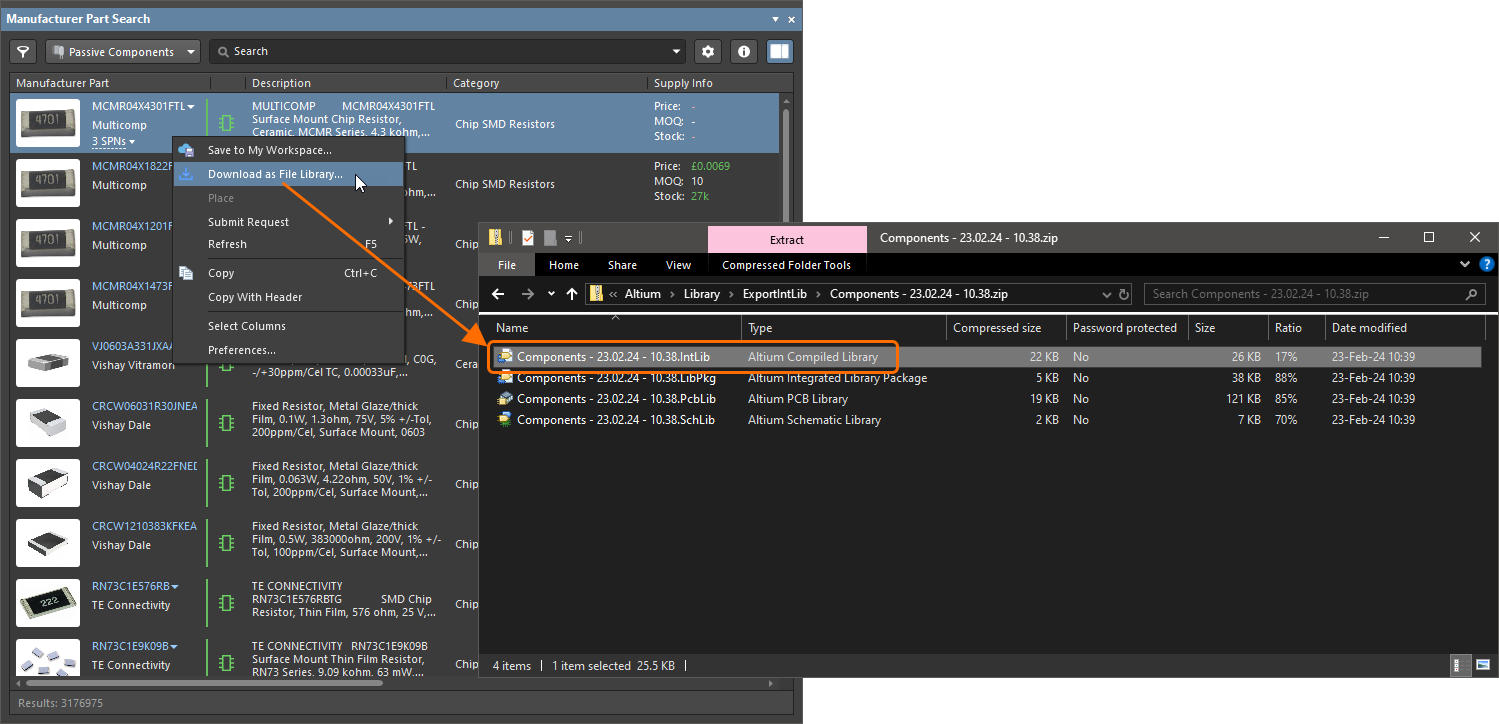

ダウンロードした Manufacturer Part Zip へコンパイル済み IntLib を追加

Manufacturer Part Search パネルからコンポーネントをファイルライブラリとしてダウンロードした時、コンパイル済み統合ライブラリ (*.IntLib) が Zip ファイルの一部として含まれるようになりました。

インポート/エクスポートの改善

Xpedition ライブラリのインポートの機能強化

このバージョンでは、Xpedition ライブラリを Altium Designer へインポートする時に以下の改善を追加しています。

- Xpedition ライブラリ内のフットプリントで定義された 'Round Donut' パッド形状を対応しました。この最初のステップにより、そのようなフットプリントパッドを (カスタムパッド形状として) インポートできることに注意してください。PCB/PCB フットプリントエディタには専用の ‘Round Donut’ パッド形状はありません。

- Xpedition ライブラリをインポートする時、定義されたパッド穴の許容差が含まれるようになりました。

- Xpedition ライブラリをインポートする時、フットプリント (つまり、取り付け穴 'A') 内の複製されたテキストストリングを対応しました。元のストリング、その複製、および関連するパラメータがインポートされます。

- Xpedition ライブラリをインポートする時、Placement Outline layer 上のフットプリントに定義された幅ゼロのラインを対応しました。

回路シミュレーションの改善

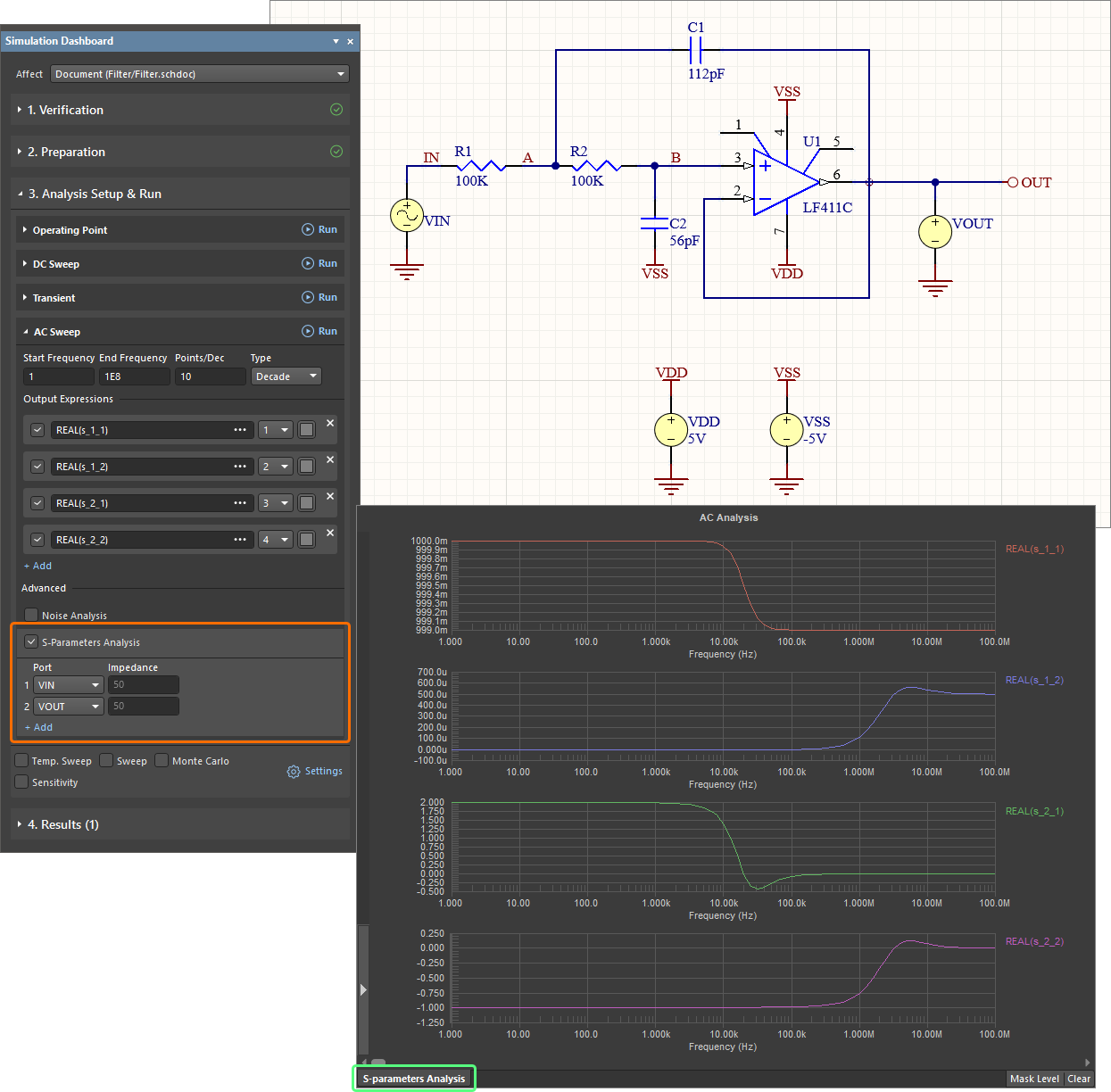

シミュレーション S パラメータ解析 (Open Beta)

このバージョンでは、S パラメータ (散乱パラメータ) の解析を実行する機能を追加しました。このようなパラメータは、入射マイクロ波と反射マイクロ波の比率 (テスト対象デバイスの場合、あるポートから別のポートへ通過する電力の量、および反射される電力の量) に基づいてネットワークを記述する方法を容易にします。これらの比率は、入力インピーダンス、周波数応答、絶縁などの回路の特性を計算するために使用できます。このタイプの解析は主に RF 回路とコンポーネントを対象としていますが、少なくとも 2 つのソース (ポート) を持つあらゆる回路にも同様に役立ちます。

この新しい解析は、Simulation Dashboard パネルの AC Sweep 領域で S-Parameters Analysis オプションを有効にすることで実行されます。関連するポート (ソース) を定義し、それぞれのインピーダンスを設定します (デフォルトは 50 オーム)。デバイスに 3 つ以上のポートがある場合、これらを適宜、追加して定義できます。これにより、結果として得られる ‘S-matrix’ に含まれる S パラメータが増加します。AC スイープ解析が実行されると、S パラメータ データが SDF ドキュメントの S-parameters Analysis チャートで利用できるようになります。

シミュレーション エンジンは、Y-パラメータ (アドミタンス) と Z-パラメータ (インピーダンス) も計算し、必要に応じて、チャート内のプロットへ追加できます。

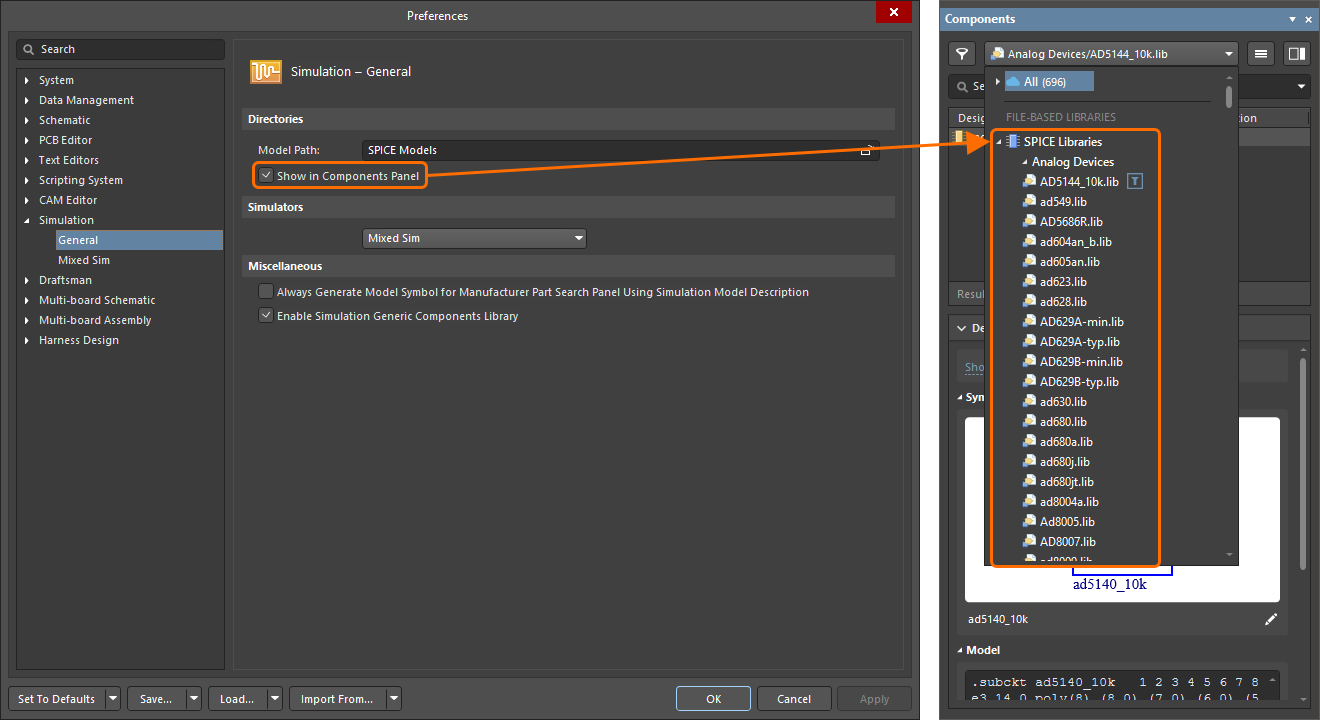

Components パネルに SPICE モデルを表示する機能を追加

このバージョンでは、新しい Show in Components Panel オプションを Preferences ダイアログの Simulation – General ページへ追加しました。このオプションを有効にすると、Components パネルで SPICE Libraries カテゴリを利用でき、Preferences ダイアログの Simulation – General ページで指定された Model Path フォルダに含まれるライブラリがこのカテゴリにリスト表示されます。カテゴリ構造は、指定されたフォルダの構造が反映されます。

この一環として、Analog Devices の SPICE モデルのフォルダを、Mixed Simulation 拡張機能のデフォルトのインストール Library フォルダ (\ProgramData\Altium\Altium Designer <GUID>\Extensions\Mixed Simulation\Library\SPICE Models\Analog Devices) へ追加しました。

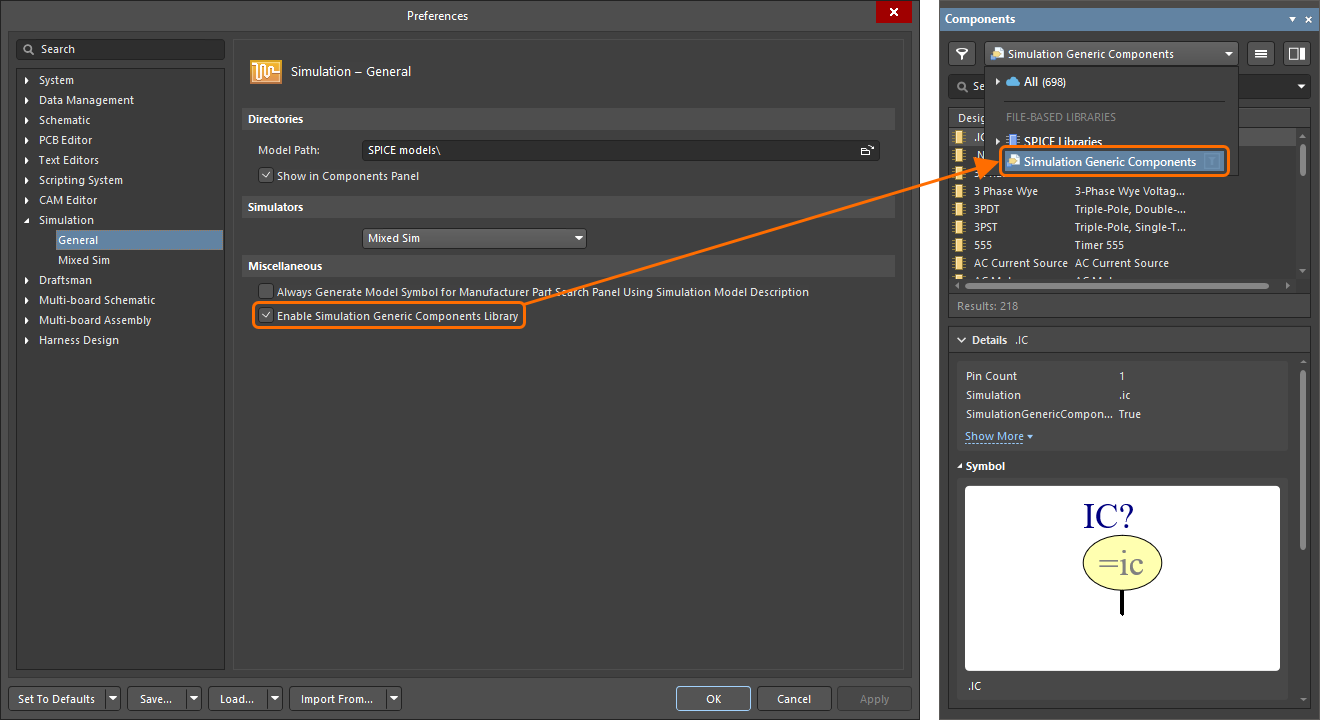

Enable Simulation Generic Components Library オプションを追加

新しい Enable Simulation Generic Components Library オプションを Preferences ダイアログの Simulation – General ページへ追加し、Components パネル内でライブラリの表示をコントロールできます。

更に、ライブラリは Libraries Preferences ダイアログ の Installed タブから削除しました。

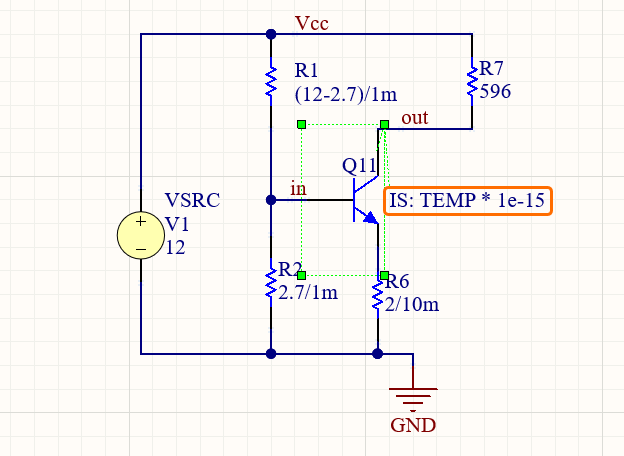

定数パラメータに 'TEMP' キーワードを対応

温度解析の場合、キーワード TEMP を定数パラメーターで使用できるようになりました。

キーワード

TEMP は、定数パラメータで使用できます。この画像は、トランジスタ Q11 の IS パラメータを計算するために使用される TEMP キーワードを示しています。

TEMP 値 (回路の実際の動作温度 (℃)) は、Simulation Dashboard パネルの Analysis Setup & Run 領域で Settings をクリックしてアクセスする、Advanced Analysis Settings ダイアログの Advanced タブで設定します。

LTspice 'AKO' モデル キーワードを対応

別のモデルに基づいてモデルを作成する時、AKO モデル キーワードを使用できるようになりました。

以下に示す例では、モデル QP にはモデル QP350 と全て同じパラメータがありますが、BF が変更され、VA が設定されている点が異なります。

.MODEL QP350 PNP(IS=1.4E-15 BF=70 CJE=.012P CJC=.06P RE=20 RB=350 RC=200)

.MODEL QP AKO:QP350 PNP(BF=150 VA=100)

Altium Designer 24.3 で完全に公開された機能

以下の機能は、このバージョンで正式に公開されました:

- Print Not Fitted Components – 22.3 から利用可能

- Any Angle Retrace – 23.10 から利用可能

- Replication of PCB Layout – 23.11 から利用可能

- Automatic Tuning of Multiple Nets – 23.11 から利用可能

- Any Angle Diff Pair Router – 24.0 から利用可能

- Ability to Store TrueType Fonts – 24.1 から利用可能

Altium Designer 24.2

リリース日: 2024年2月15日 – バージョン 24.2.2 (build 26)

Altium Designer 24.2.2 のリリースノート

PCB デザインの改善

複製中にコンポーネントを手動で選択する機能を追加

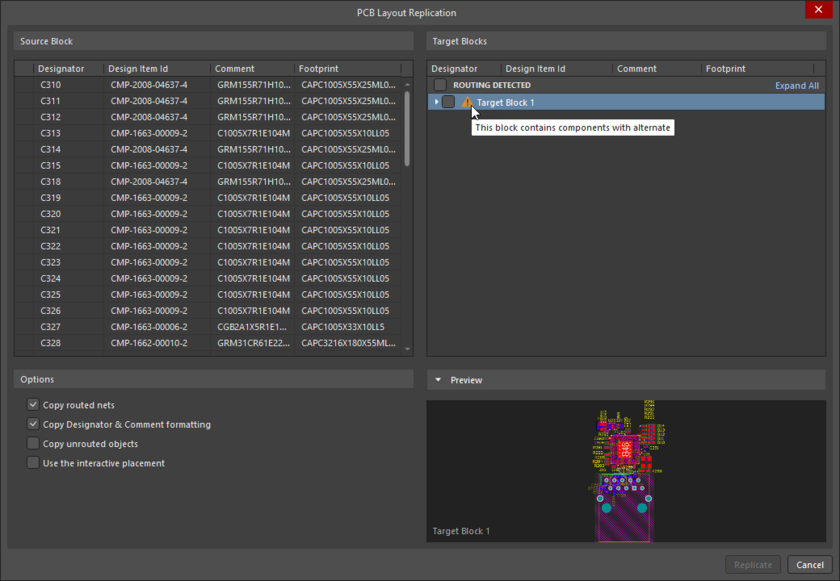

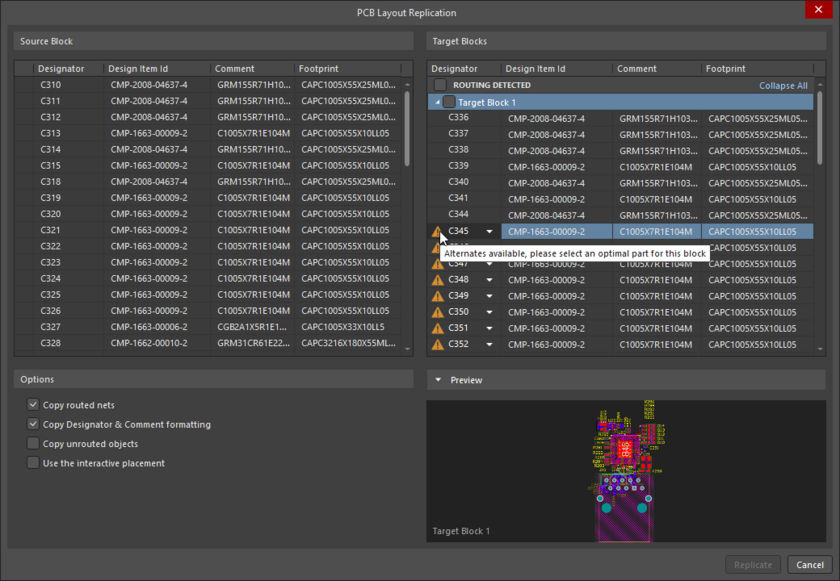

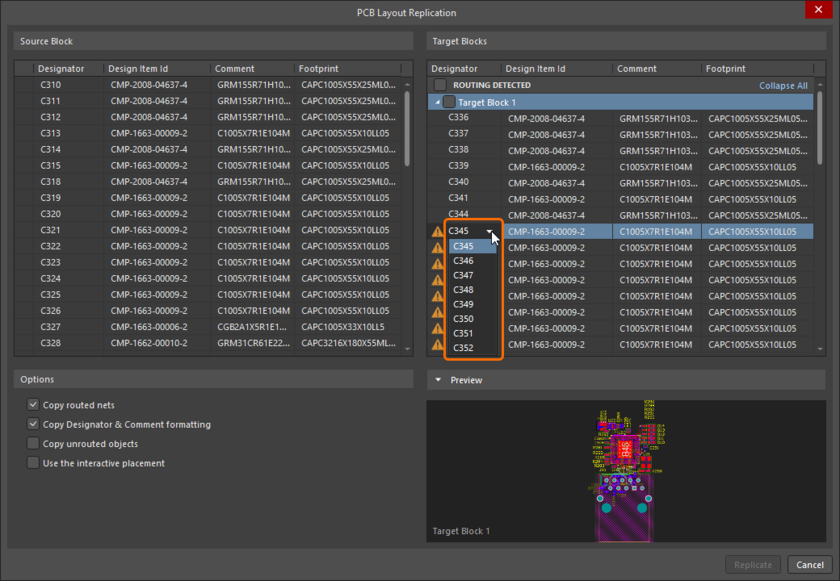

このバージョンでは、PCB Layout Replication ツールの機能を拡張し、ツールによって複数のコンポーネントが同様の接続を持つと検出された目的のブロックにコンポーネントを手動でマッピングできるようになりました。これにより、回路接続を侵害することなくコンポーネント (相互に忠実に置き換えることができる) 間で手動で選択することができます。

同様の接続を持つ複数のコンポーネントがこのツールによって検出された場合、PCB Layout Replication ダイアログ内の対応する目的のブロックには ![]() アイコンが表示され (ブロックが折りたたまれている時)、利用可能な置換がある各コンポーネントには

アイコンが表示され (ブロックが折りたたまれている時)、利用可能な置換がある各コンポーネントには ![]() アイコンが表示されます (ブロックが展開されている時)。置換が検出されたコンポーネントの Designator 欄のドロップダウンを使用して、必要なコンポーネントを選択します。

アイコンが表示されます (ブロックが展開されている時)。置換が検出されたコンポーネントの Designator 欄のドロップダウンを使用して、必要なコンポーネントを選択します。

| ❯❮ |

レイヤ構成マネージャの差動ペア コモンモード インピーダンスを追加

差動ペアのインピーダンス プロファイルを定義するために、Properties パネルの Type として Differential が選択されている時、選択したインピーダンス プロファイルのコモンモード インピーダンスを表示する欄を追加しました。Impedance (Zcomm) として表示されるこの値は、Simbeor の計算された伝送線路データから取得されます。

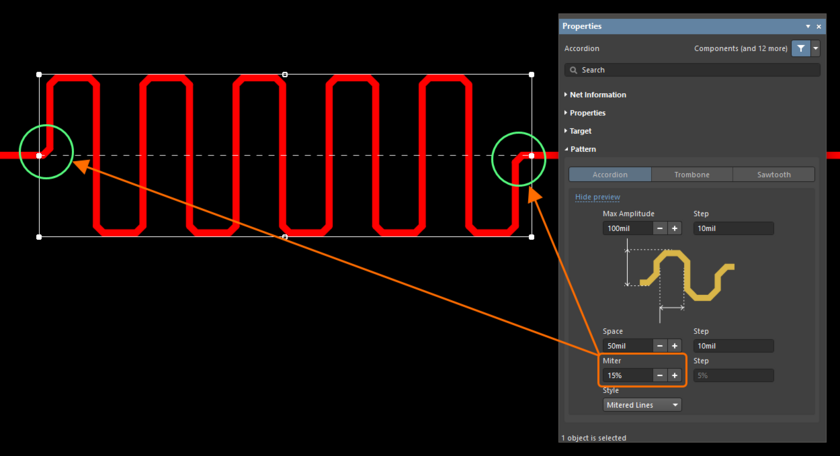

アコーディオンを配線へ接続するためのチューニング MITER パラメータの使用

アコーディオンを追加して配線の長さをインタラクティブに調整する時、Properties パネルでアコーディオンに対して定義された Miter パラメータは、アコーディオンを配線へ接続するトレースの miter にも使用されるようになりました。以前は、インタラクティブ配線用に定義された Miter Ratio パラメータがこれらのトレースに使用されていました。

アコーディオン プロパティの Miter 値が、そのアコーディオンを配線に接続するトレースにも適用されるようになりました。

制約マネージャの改善

制約を PCB から回路図へ移行する機能の強化

このバージョンでは、制約マネージャ の Physical と Electrical ビューで定義された制約を移行する機能を追加しました。PCB エディタで、メインメニューから Design » Update Schematics in <PCBProjectName> コマンドを選択し、Engineering Change Order ダイアログを使用して制約の変更を調査、確認、実行できます。

マルチボードデザインの改善

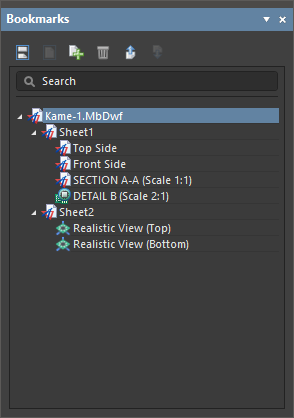

マルチボード Draftsman ドキュメント用の Bookmarks パネルを追加

マルチボードデザイン (*.MbDwf) の製造図で作業している時、Draftsman で Bookmarks パネルを使用できるようになりました。このパネルには、Draftsman ドキュメントのシートのツリービューが表示されます。各シートエントリは展開したり折りたたむことができます。展開すると、下図に示す様に、各シートの適切な内容が表示されます。

パネルを使用すると、デザインスペース内を容易に移動できます。パネル、またはデザインスペースで item を選択すると、Properties パネル (開いている場合) には、選択した item のプロパティや設定が表示されます。更に、Bookmarks パネルで item を選択すると、選択した item がデザインスペースでズーム表示されます。

ハーネスデザインの改善

ケーブル、シールド、ツイスト オブジェクトの重複したデジグネータ違反を削除

Wiring Diagram (配線図) では、ケーブル/シールド/ツイスト オブジェクトで同じデジグネータが使用されていても、Duplicate Designator (WD) violation check では問題としてレポートされません。これは分割し、同じデジグネータを使用して別の場所で使用できるようになりました。

ツイストとシールド用のワイヤーをハイライト表示

ツイスト/シールドが Wiring Diagram 上の複数の場所のワイヤに関連付けられている場合 (同じデジグネータを使用して)、ツイスト/シールドのインスタンスを選択すると、グループ内の関連する全てのワイヤがネオングリーンでハイライト表示されます。

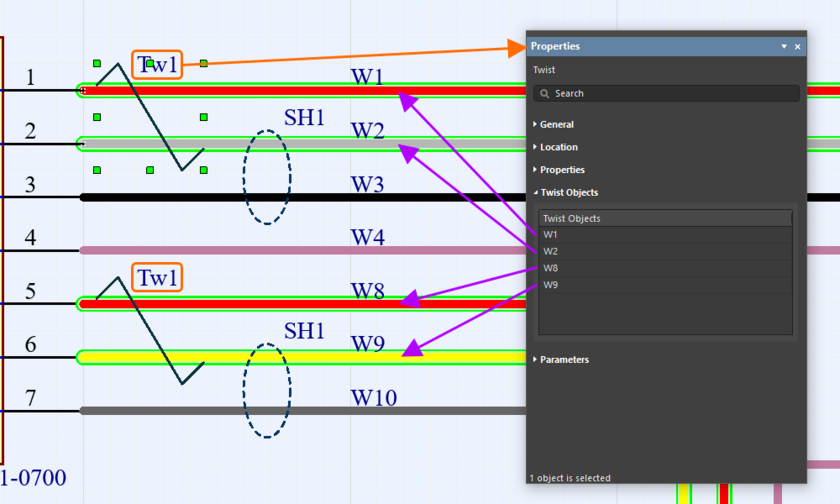

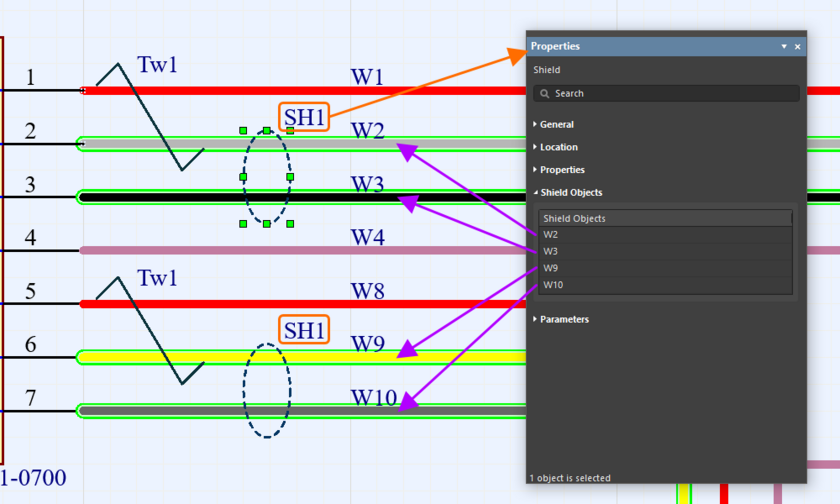

| ❯❮

同じデジグネータを持つ 2 つのツイストが異なるワイヤのグループに配置されている Wiring Diagram の例。これらのツイストの内 1 つだけが選択されている場合、これらのツイストによって覆われている全てのワイヤがハイライト表示されます。

同じデジグネータを持つ 2 つのシールドが異なるワイヤのグループに配置されている Wiring Diagram の例。これらのシールドの内 1 つだけが選択されている場合、これらのシールドで覆われている全てのワイヤがハイライト表示されます。 |

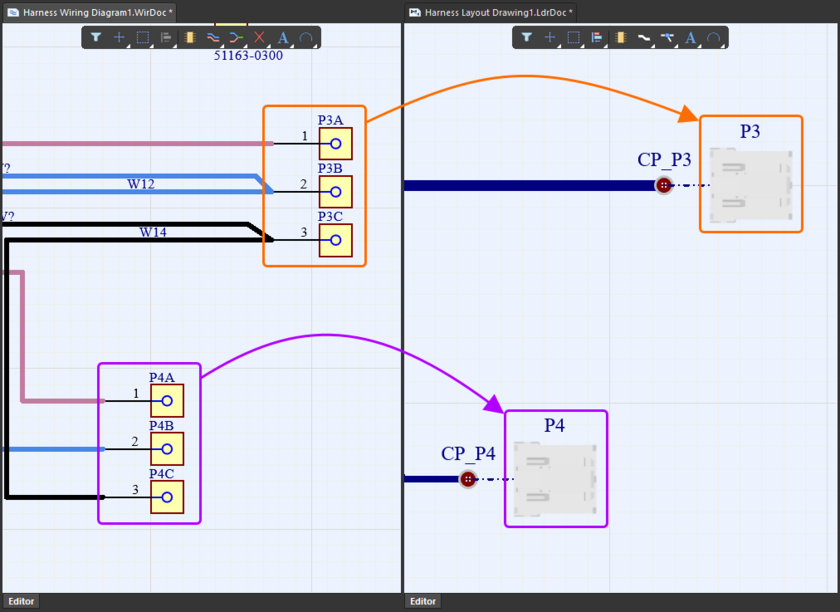

マルチパート コンポーネントの対応

マルチパート コンポーネント データを Wiring Diagram から Layout Drawing (レイアウト図) へ移行する機能を追加しました。マルチパート コンポーネントが Wiring Diagram に配置されている時、デジグネータは Layout Drawing 内のコンポーネントへ正しく割り当てられます。同じコンポーネントの複数の部品が Wiring Diagram に配置されている場合、コンポーネントのインスタンスは 1 つだけ Layout Drawing に配置されます。

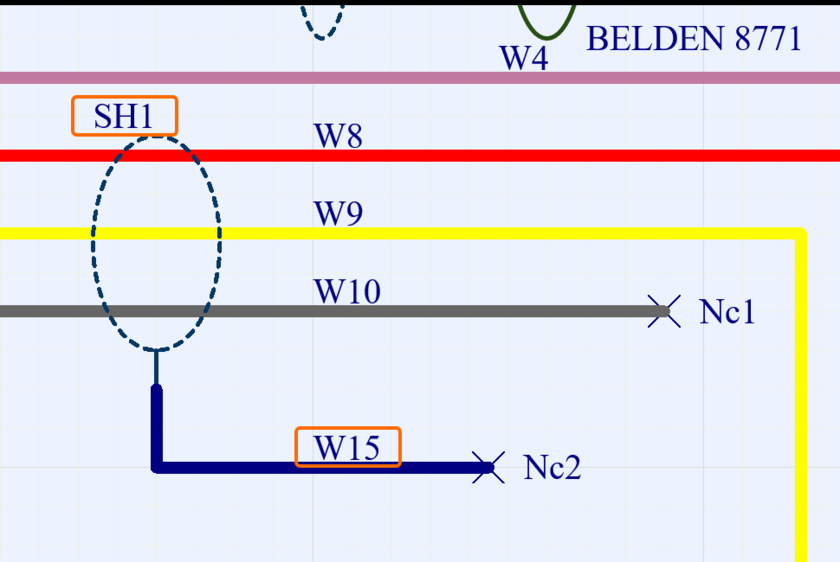

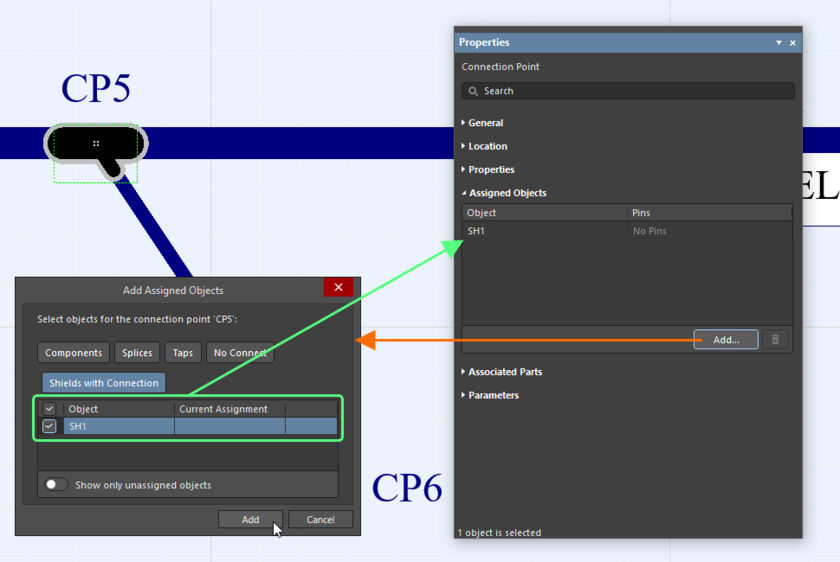

シールドを接続点へ接続する機能を対応

Wiring Diagram で定義された接続オブジェクトを持つシールドを、Layout Drawing の接続点へ割り当てることができるようになりました。接続点が選択されている時、Add Assigned Objects ダイアログ (Properties パネルの Assigned Objects 領域にある Add ボタンをクリックして表示) を使用して、その接続点へ割り当てる接続を持つシールドを選択できます。

| ❯❮ |

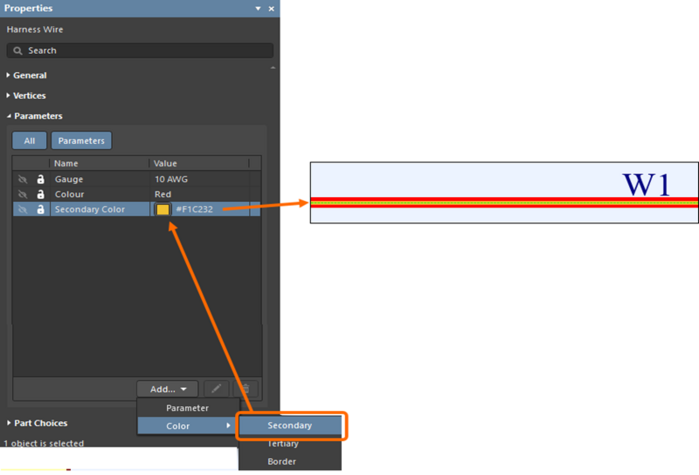

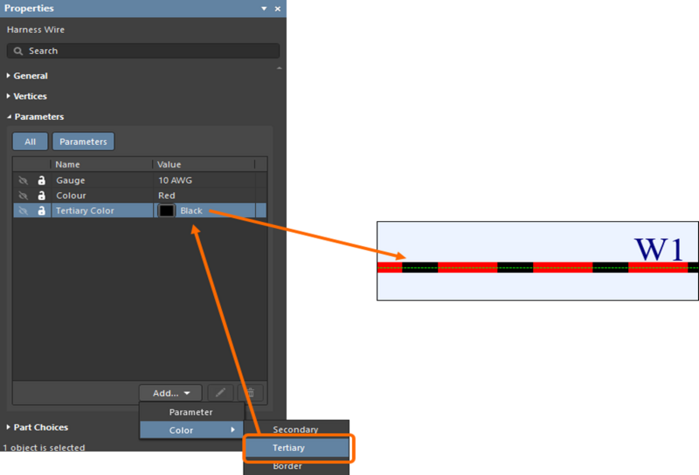

多色ワイヤの対応

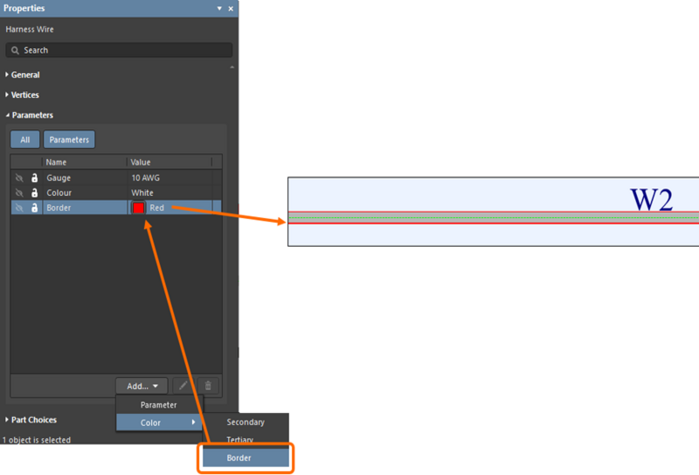

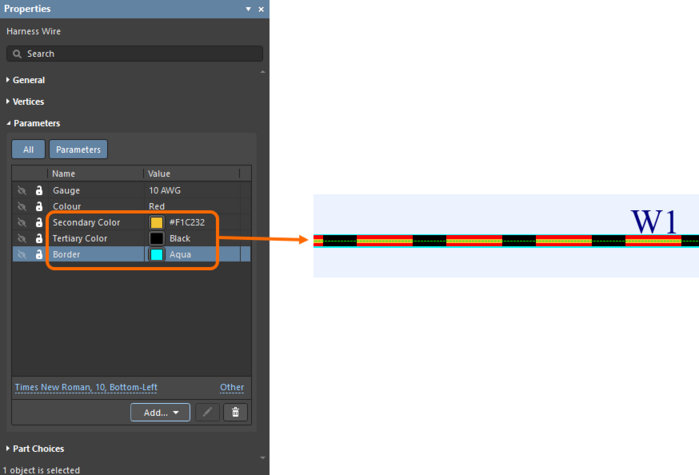

ワイヤの 2 番目と 3 番目の色を選択することにより、Wiring Diagram で多色のワイヤを対応するようになりました。(原色は、配置されたワイヤの色です。) Properties パネルで、Parameters 領域の下部にある Add ドロップダウンをクリックし、Secondary と Tertiary を選択して目的の色を定義します。選択した色のパラメータが Parameters 領域に表示されます。パネル内の色アイコンをクリックして、色のオプションを開きます。目的の色をクリックします。同じドロップダウンを使用して Border を選択し、ワイヤの境界線の色を定義することもできます。以下のスライドショーをクリックして例をご覧ください。

| ❯❮

2 番目の色が定義されたワイヤ

3 番目の色が定義されたワイヤ

境界線の色が定義されたワイヤ

全ての色オプションが定義されたワイヤ |

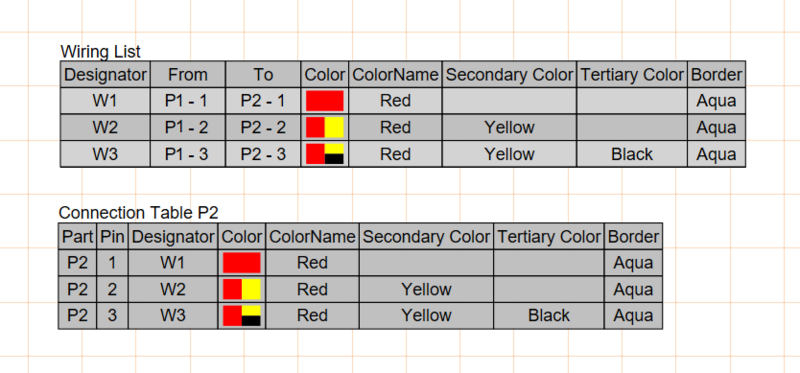

多色のワイヤは、ハーネスデザインの Draftsman ドキュメント (*.HarDwf) でも対応しています。2 番目、3 番目、境界線の色に関する追加の列を配置されたテーブルに表示でき、対応する Color のセルが分割されて、ワイヤへ割り当てられた 2 番目と 3 番目の色が表示されます。

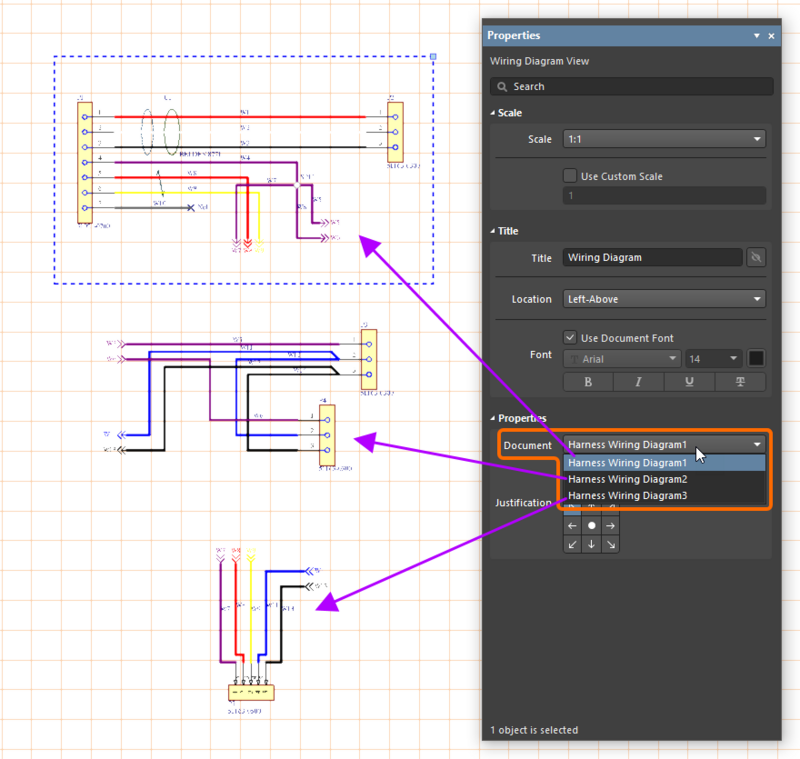

Draftsman ドキュメント内の複数の Wiring Diagrams の対応

Harness Draftsman ドキュメント (*.HarDwf) は、同じプロジェクト内の複数の Wiring Diagram ドキュメント (*.WirDoc) を対応するようになりました。この機能を使用すると、配置された wiring diagram ビューを生成、および更新する wiring diagram ドキュメントを選択できます。wiring diagram ビューが選択されている時、Properties パネルの Properties 領域にある Document ドロップダウンを使用して、このビューの wiring diagram ドキュメントを選択します。

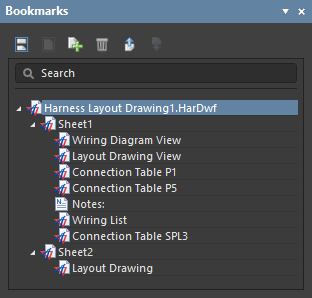

ハーネス Draftsman ドキュメント用の Bookmarks パネルを追加

ハーネスデザイン (*.HarDwf) の製造図で作業している時、Draftsman で Bookmarks パネルを利用できるようになりました。このパネルには、Draftsman ドキュメントのシートのツリービューが表示されます。各シートのエントリは展開したり折りたたむことができます。展開すると、下図に示す様に、各シートの適切な内容が表示されます。

パネルを使用すると、デザインスペース内を容易に移動できます。パネル、またはデザインスペースで item を選択すると、Properties パネル (開いている場合) には、選択した item のプロパティや設定が表示されます。更に、Bookmarks パネルで item を選択すると、選択した item がデザインスペースでズーム表示されます。

データ管理の改善

SiliconExpert の強化

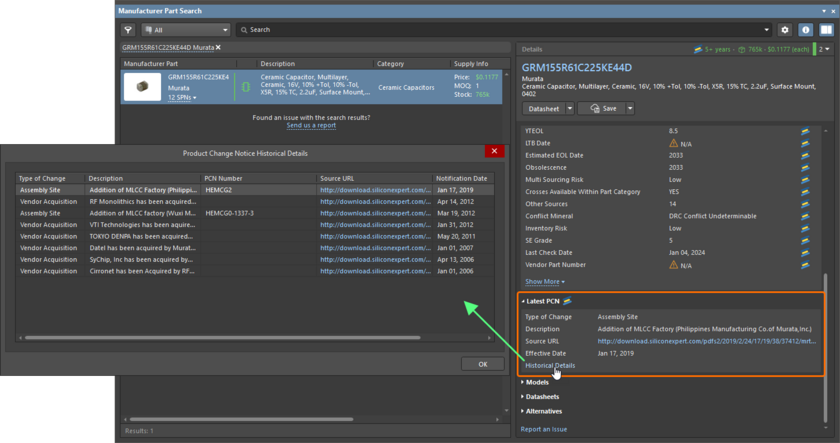

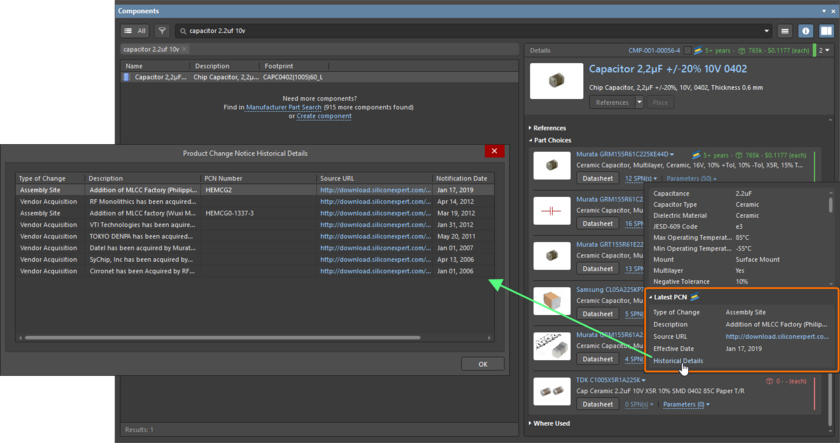

SiliconExpert の Product Change Notice を追加

SiliconExpert が提供する Product Change Notice (PCN) を、Manufacturer Part Search パネルと、part choices にアクセスできる全ての場所に追加しました。デフォルトでは、最新の PCN データが表示されます。Historical Details コントロールを使用して Product Change Notice Historical Details ダイアログを開き、以前の PCN の詳細を参照できます。

| ❯❮

Manufacturer Part Search パネルから最新、および過去の PCN にアクセス。

part choice から最新、および過去の PCN にアクセス (ここでは、Components パネルが例として示されています)。 |

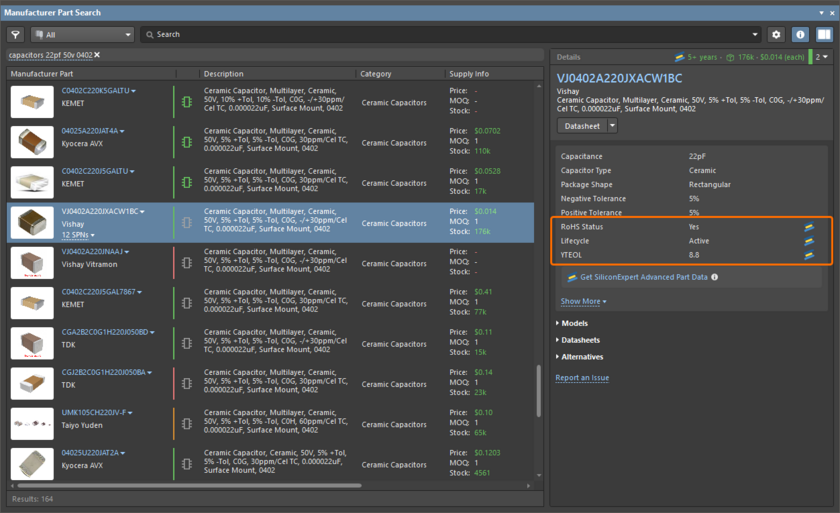

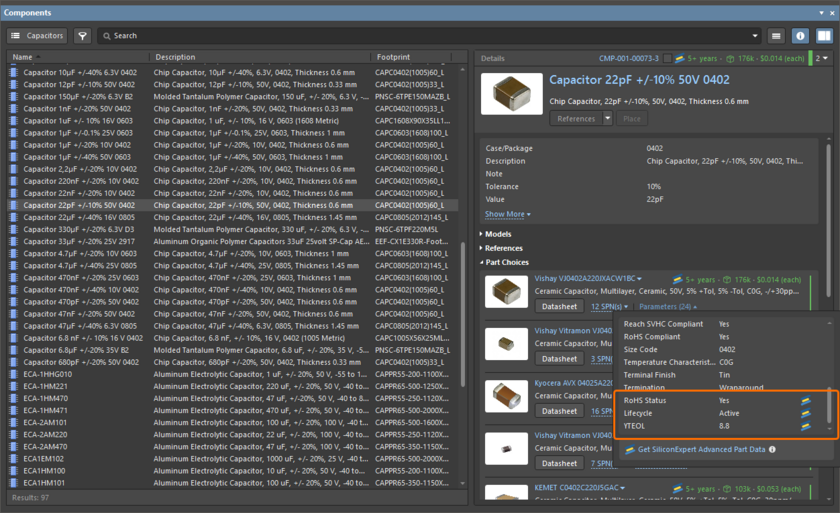

SiliconExpert の '無償' パラメータの対応

SiliconExpert が提供する Lifecycle、YTEOL、RoHS Status パラメータが、Manufacturer Part Search パネルと part choices が表示される全ての場所にデフォルトで表示されるようになりました。従って、これらの '無償' パラメータにアクセスするために、この部品のデータをリクエストする必要はありません (そのため、SiliconExpert パッケージの割り当てを使用)。

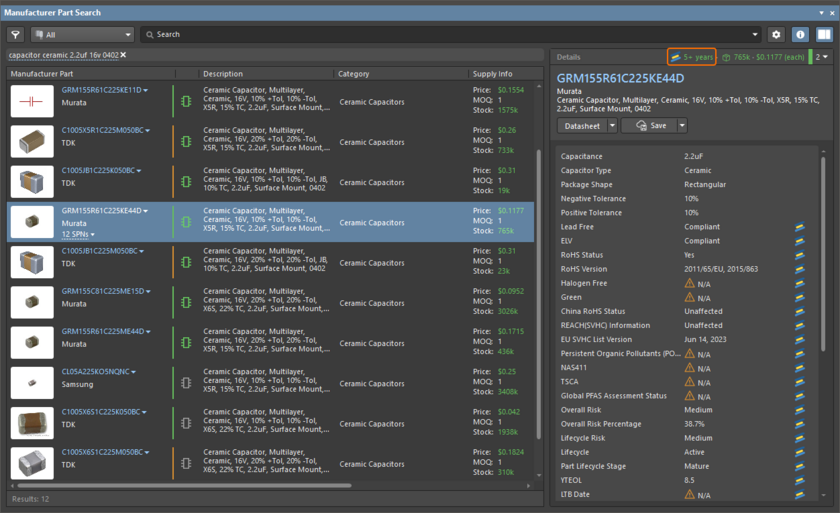

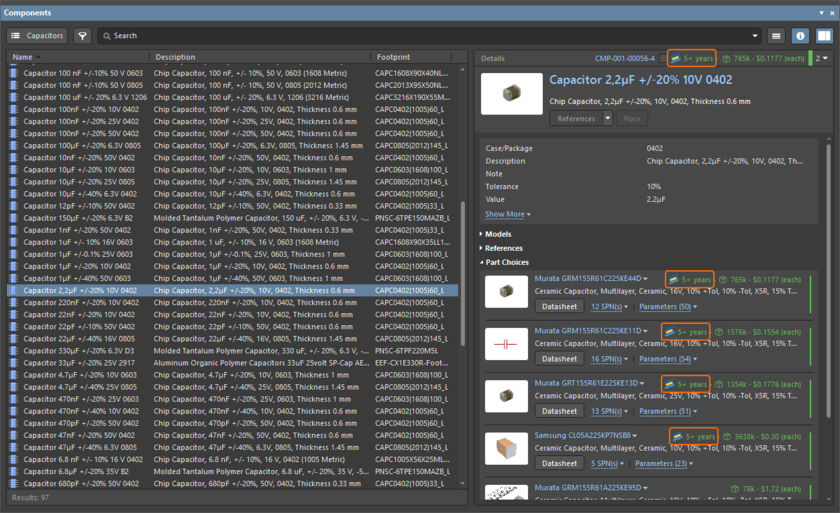

| ❯❮

Manufacturer Part Search パネルから SiliconExpert が提供する '無償' パラメータにアクセス。

part choice から、SiliconExpert が提供する '無償' パラメータにアクセス (ここでは、Components パネルが例として示されています)。 |

また、これらの SiliconExpert の '無償' パラメータは、他の全ての SiliconExpert パラメータを要求せずに、ActiveBOM (対応する列を ActiveBOM ドキュメントにへ追加して) で使用できます。

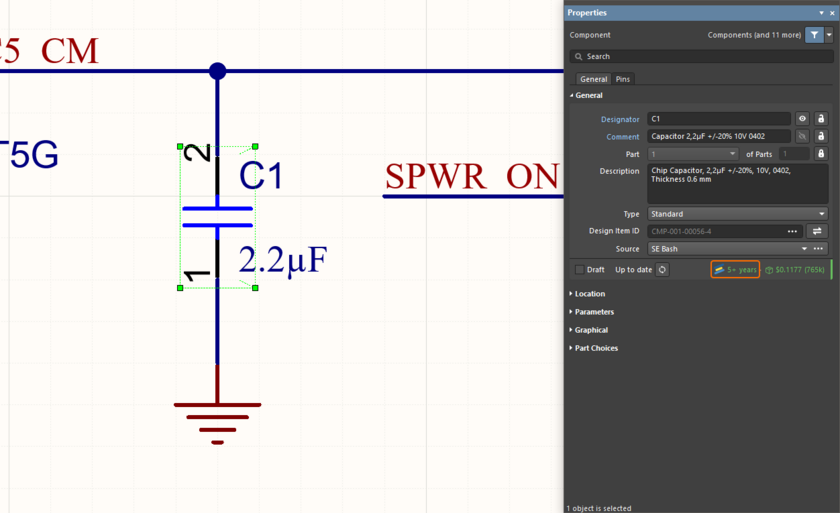

YTEOL パラメータの表示を追加

YTEOL パラメータが以下の場所に表示されるようになりました:

- Manufacturer Part Search パネルで manufacturer part が選択された時の Details ペインのヘッダ。

- Components パネルでコンポーネントが選択されている時の、Details ペインのヘッダ。

- part choices が表示される全ての場所。

- 回路図シート上に配置されたコンポーネントが選択されている時の Properties パネル。

| ❯❮

Manufacturer Part Search パネルで YTEOL パラメータを表示。

Components パネルの part choices で YTEOL パラメータを表示。

選択したコンポーネントの Properties パネルで YTEOL パラメータを表示。 |

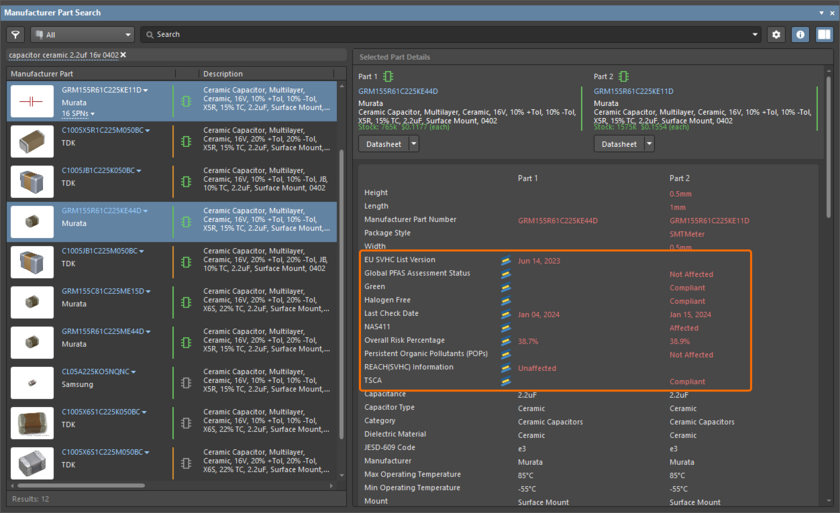

Manufacturer Parts を比較する際の SiliconExpert パラメータの対応

SiliconExpert パラメータは、選択した 2 つの部品を比較する時、Manufacturer Part Search パネルの Selected Part Details ペインで対応するようになりました。

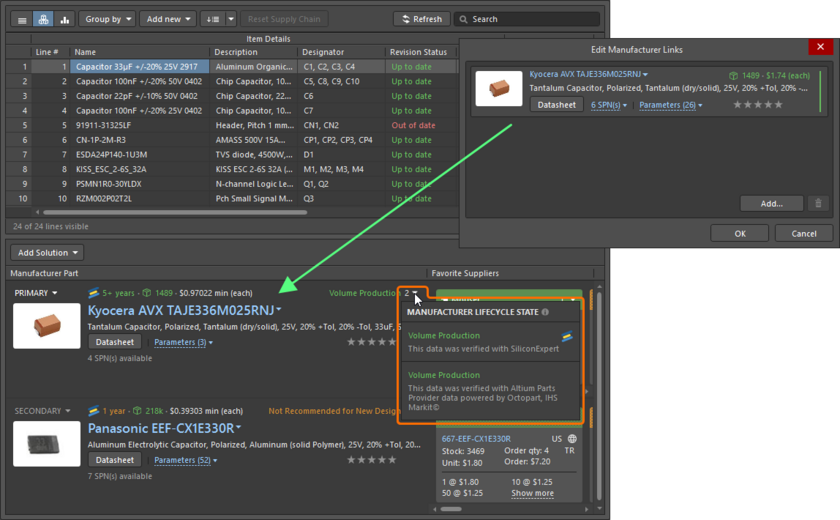

集約されたライフサイクルを Manufacturer Links へ対応

ActiveBOM ドキュメントへの manufacturer link の形式で追加されたソリューションを探す時、その manufacturer link (Octopart、または IHS Markit®、および SiliconExpert を利用した Altium Parts Provider) のライフサイクル データのソースが複数ある場合、利用可能な全てのソースにあるライフサイクル情報がリンクからアクセスできるようになりました。manufacturer lifecycle state 上にカーソルを置くか、ドロップダウンを使用して、ツールチップ/ポップアップ内の全てのソースからのライフサイクル情報を表示できます。

インポート/エクスポートの改善

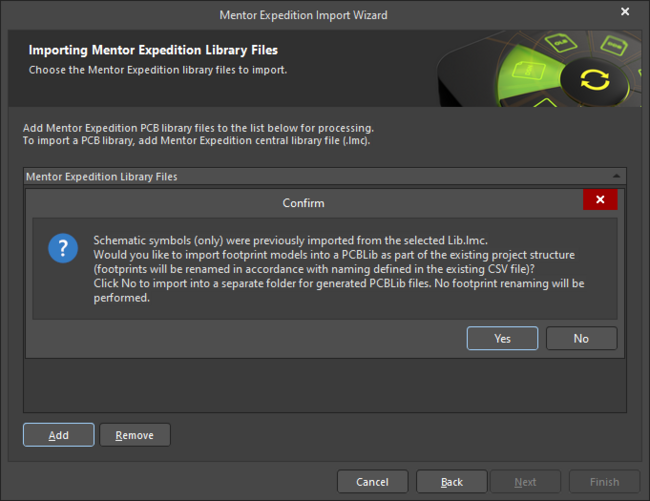

XPedition の既存のプロジェクト構造へフットプリントをインポート

以前に xDX Designer インポート ウィザード を使用して Import Symbols Only オプションを有効にして回路図シンボル (のみ) をインポートした Xpedition ライブラリ (*.lmc) の場合、既存のプロジェクト構造の一部としてフットプリント モデルを PCBLib へインポートすることを選択できるようになりました。フットプリントの名称は、xDX Designer インポート プロセスの一部として生成された既存の CSV ファイルで定義された名称に従って変更されます。

インポート ウィザード の Importing Mentor Expedition Library Files ページで Xpedition ライブラリファイルを追加する時、以前にインポートされたライブラリが検出された場合、上記の様にフットプリントをインポートするかどうかを確認するダイアログが表示されます。No をクリックすると、フットプリントは生成された PCBLib ファイル用の別のフォルダへインポートされ、フットプリントの名称変更は実行されません。

ALTIUM DESIGNER 24.2 で完全に公開された機能

以下の機能は、このバージョンで正式に公開されました:

- PCB Section View - 23.5 から利用可能

Altium Designer 24.1

リリース日: 2024年1月16日 – バージョン 24.1.2 (build 44)

回路図の改善

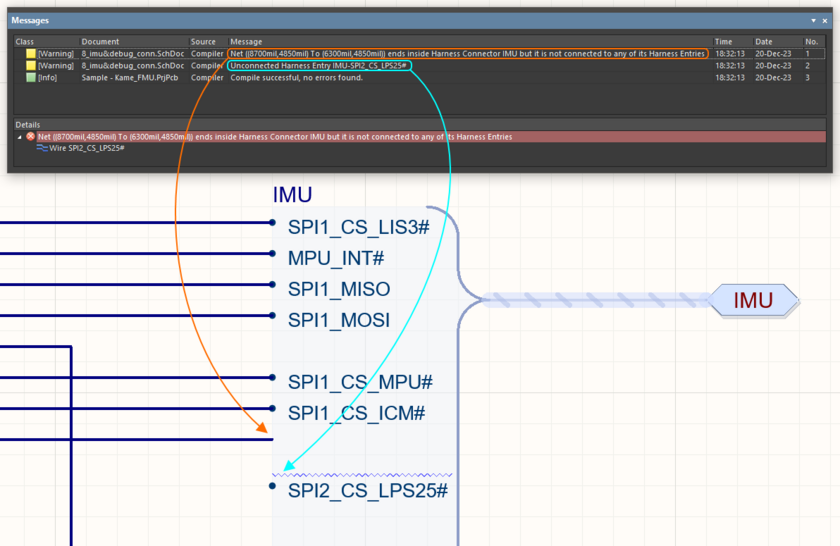

ハーネスコネクタへ接続されたオブジェクトの違反チェックを追加

このバージョンでは、PCB デザインプロジェクトの回路図内の シグナルハーネス に関連する違反を検出するための新しい違反チェックを追加しました:

- Invalid Connection to a Harness Connector 違反チェックでは、ワイヤ、バス、またはシグナルハーネスがハーネスコネクタ内に含まれている、またはハーネスコネクタの端へ接続されているが、ハーネスエントリへ接続されていない状況が検出されます。

- Unconnected Harness Entry 違反チェックでは、未接続のハーネスエントリが検出されます。

これらの違反タイプの設定は、Project Options ダイアログの Error Reporting タブ にある Violation Associated with Harnesses グループにあります。

PCB デザインの改善

パッド穴クリアランスチェックの改善 (Open Beta)

このバージョンでは、annular ring の無いパッドからのクリアランスを検出する動作を改善しました。

パッドの穴サイズがパッドサイズ以上か、またはパッドサイズと同じ (従って、annular ring が無い) 場合、Hole と TH Pad クリアランスの最大値ではなく、制約マネージャ の該当する制約、または Clearance デザインルール によって Hole に定義されたクリアランス値が適用されます。

| ❯❮

新しいパッド穴のクリアランス動作の例。制約マネージャ で設定されたクリアランス。

新しいパッド穴のクリアランス動作の例。Clearance デザインルールで設定されたクリアランス。 |

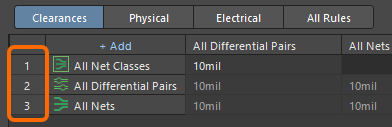

新しく作成された Clearance 制約、および Clearance デザインルールの Hole クリアランスのデフォルト値が 10mil / 0.254mm の値に更新されていることに注意してください。

TRUETYPE フォントを保存する機能 (Open Beta)

このバージョンでは、TrueType フォントを使用するテキストオブジェクトのジオメトリを PCB ドキュメント内に自動で保存する機能を追加しました。PCB ドキュメント内のオブジェクト (テキストストリング/フレーム、寸法線、ドリルテーブル、レイヤ構成テーブル) で TrueType フォントを使用している場合、これらのオブジェクトは、PCB ドキュメントを別のコンピュータで開いた時、同じフォント ジオメトリを使用して表示されます (TrueType フォントがインストールされてなくても)。

欠落しているフォントを使用するオブジェクトを選択すると、Properties パネルの上部に警告メッセージが表示されます。テキストに影響を与えるオブジェクト (例えば、text height、またはテキスト自体) のプロパティを変更すると、Missing fonts ダイアログが開き、置換フォントを選択できます。

このダイアログは、PCB List パネルからテキスト関連のプロパティを変更する時にも表示されます。

異なる欠落しているフォントを使用して複数のオブジェクトを編集しようとすると、ダイアログで欠落しているフォントごとに代替フォントを選択できます。

強化した Pad Properties パネル

Pad Properties パネルの Pad Stack 領域を強化し、使い易さを向上しました。項目を選択すると、その項目名が青色でハイライト表示され、項目全体が背景とは異なる色合いで表示されます。

PCB CoDesign の改善

カテゴリの変更をハイライト表示する機能

PCB CoDesign パネルで Show on PCB オプションを有効にすると、パネルの変更リストで特定のカテゴリが選択されている時に、そのカテゴリ内の全ての変更をハイライト表示できるようになりました。

ユニオンによるグループ化の変更

ユニオン (PCB 上のプリミティブのグループ) の比較、および変更の適用を対応しました。ユニオン関連の変更は、PCB CoDesign パネルの変更リストの Unions カテゴリに表示されます。また、他のカテゴリの変更は、対応するオブジェクトがいずれかに属している場合、ユニオンでグループ化されるようになりました。

'Merged' 状態への更新

PCB CoDesign パネルを使用して変更を統合した後、新たに不一致が発生するまで、PCB ドキュメントは Merged 状態 (Projects パネル内のアイコン) のままになります。変更をローカルに保存しても、その状態は Modified に変更されなくなります。

また、Merged 状態のドキュメントは、Save to Server ダイアログで Workspace へ保存できるように常に有効になっており、無効にすることはできないことに注意してください。

制約マネージャの改善

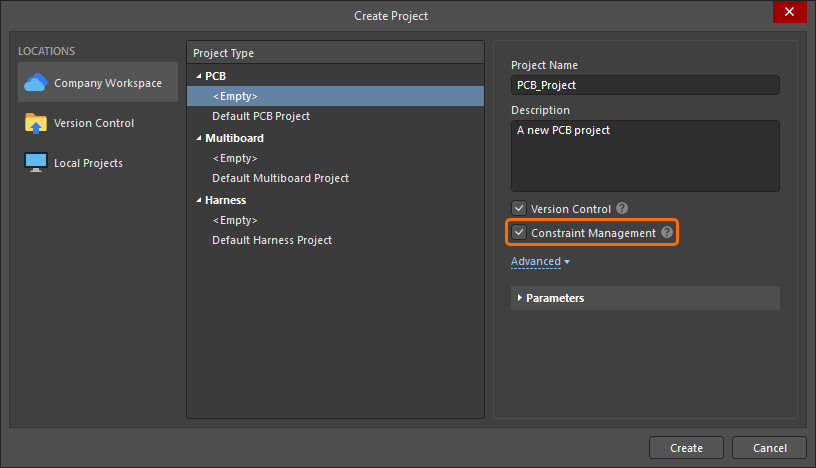

新しいプロジェクトで制約マネージャの使用を選択する機能

新しい PCB プロジェクトを作成する時、制約マネージャ を使用するか、または従来のデザインルール システムを使用するかをコントロールできるようになりました。作成中のプロジェクトで 制約マネージャ を使用するには、Create Project ダイアログ (File » New » Project) で、Constraint Management オプションを有効にします。

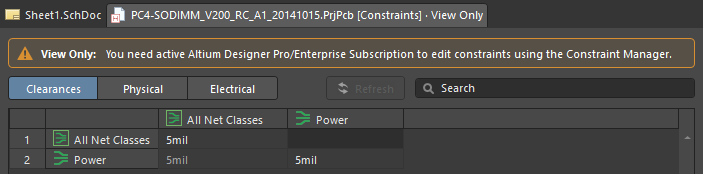

'View Only' モード

PCB プロジェクトで 制約マネージャ が有効になっている場合、Altium Designer Pro/Enterprise サブスクリプションを持たないユーザが 制約マネージャ を開くと、制約マネージャ は View Only モードで表示されます。この場合、ユーザは定義された制約を表示できますが、変更することはできません。制約マネージャ の上部にあるメッセージは、制約マネージャ が View Only モードであることを通知します。

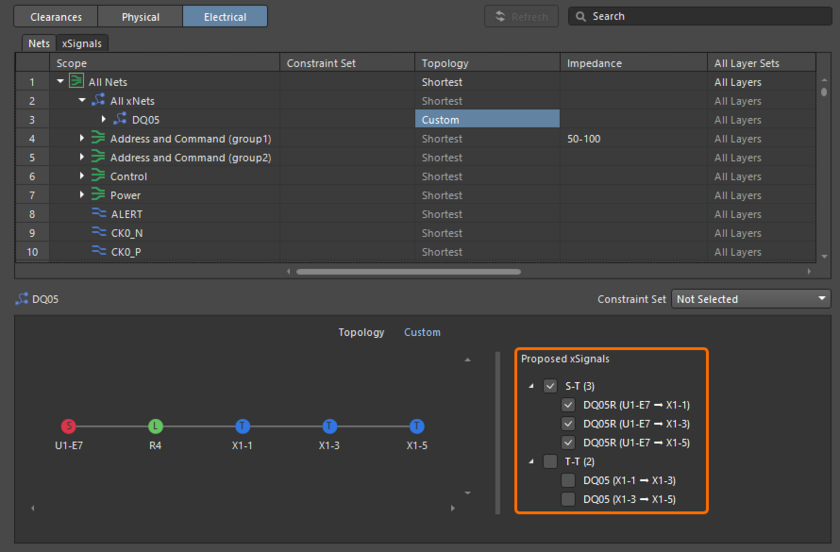

Xsignal 作成の更新

このバージョンでは、制約マネージャ を使用した xSignals の定義に関する更新があります:

- 提案された xSignal のリストは、ソースから到達点へ向かう xSignals (S-T) と、ある到達点から別の到達点へ向かう xSignals (T-T) の 2 つのグループへ分割されます。グループのチェックボックスを使用して、対応するグループ内の全ての xSignal を選択/選択解除できます。

- 提案された xSignal のリストには、ソースから各到達先へ向かう xSignal が含まれるようになりました (ソースから最も近い到達先に向かう xSignal だけではありません)。

-

提案された xSignal をより適切に表現するために、リスト内で以下の方針を使用して名称が付けられるようになりました:

<SourceNetName> (<SourcePinDesignator> → <DestinationPinDesignator>)制約マネージャ の xSignals タブ、または PCB ドキュメントに表示される作成された xSignal の名称には、以前の

<SourceNetName>_<SourcePinDesignator>_<DestinationPinDesignator>の方針が使用されることに注意してください。

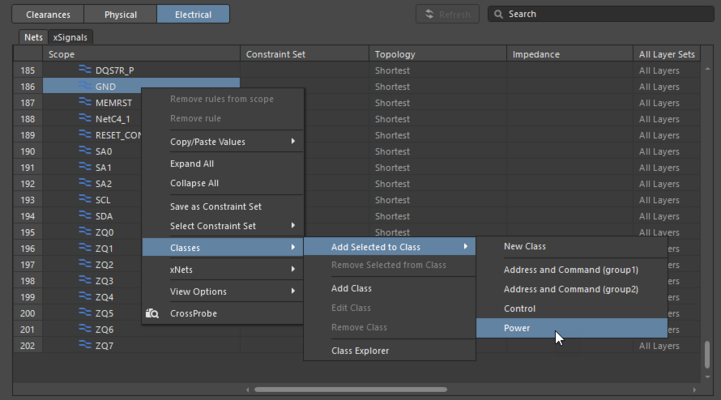

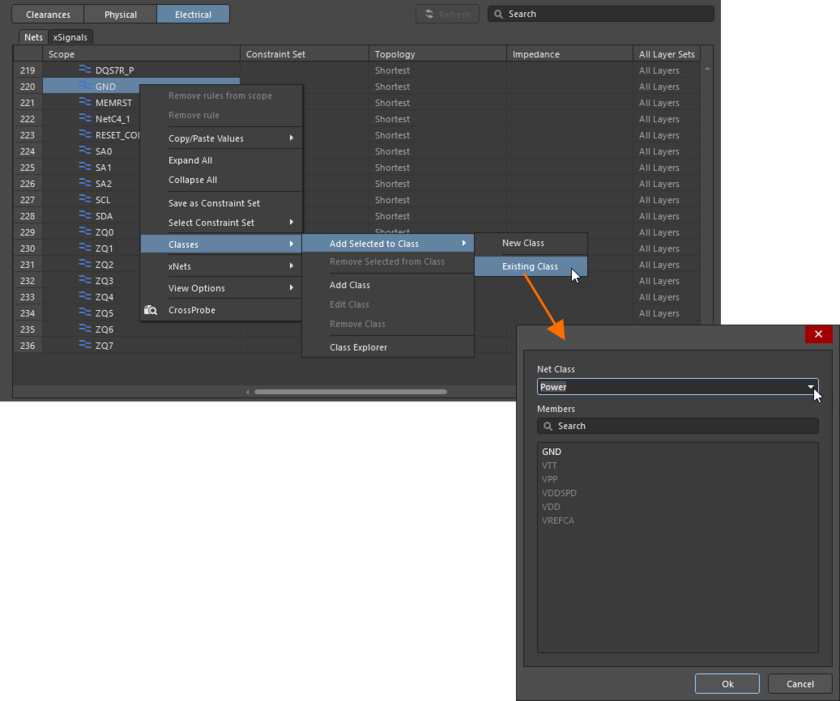

クラス選択の改善

Physical と Electrical ビューのエントリの右クリック メニューを更新し、メニューから既存のクラスへオブジェクトをすぐに追加できるようになりました。これを行うには、選択したオブジェクトを右クリックし、Classes » Add Selected to Class サブメニューから既存のクラスを選択します。

クラスが 30 個を超える場合は、クラスのリストの代わりに、Classes » Add Selected to Class » Existing Class コマンドをメニューで利用できます。このコマンドを使用してダイアログを表示し、選択したオブジェクトを追加する既存のクラスを選択できます。

表に行番号を追加

行番号を 制約マネージャ の表へ追加し、リスト内の項目をより簡単に識別して区別できるようになりました。

マルチボードデザインの改善

マルチボードプロジェクトにおける Draftsman ドキュメントの対応 (Open Beta)

Draftsman ドキュメント (*.MbDwf) をマルチボードプロジェクトへ追加して、このプロジェクトのマルチボードアセンブリの製造図を作成できるようになりました。

マルチボードプロジェクトの Draftsman ドキュメントに配置できるビューは以下の通りです:

- Multi-board view – マルチボードアセンブリを構成する PCB の外形と 3D モデルの自動化されたグラフィックの合成。

- Section view – 配置された multi-board view を通じて、指定された 'cut' 点からスライスした外形、または断面。

- Board detail view – multi-board view の定義した領域の拡大図 (フローティング)。

- Board realistic view – 現在のマルチボードアセンブリのスケーラブルな 3D レンダリング。

Draftsman の注釈、寸法線、グラフィカル ツールに加え、BOM や一般的な表も利用できます。

モジュールエントリ グループを移動する機能

マルチボード回路図ドキュメント (*.MbsDoc) で、選択したモジュールエントリのグループを移動する機能を追加しました。この新機能により、各モジュールエントリを個別に移動する必要がなくなるため、編集プロセスが高速化されます。デザインスペースで、複数のモジュールエントリを選択し、マウスの左ボタンを使用してグループを目的の場所へドラッグできます。新しい位置へドラッグされている間、各エントリに赤い点が表示されます。マウスボタンを放すと、グループを現在の場所に配置できます。

ハーネスデザインの改善

'Crimps' を 'Cavities' へ変更

Wiring Diagram (配線図) と Layout Drawing (レイアウト図) の UI で、'Crimps' の名称を 'Cavities' に変更しました。

Shield オブジェクトと Twist オブジェクトへ Designator 欄を追加

ハーネス wiring diagram の shield と twist のプロパティへ Designator 欄を追加しました。

複数シート機能用に Wire Break オブジェクトを追加

完全な Wiring Diagram を複数のシートに渡って ('flat' デザイン方式で) 定義できるようになり、それぞれが独自の *.WirDoc ドキュメントで表され、新しい Wire Break オブジェクトを使用してワイヤを分割できるようになりました。

Wire Break は、以下に示すように、Place メニュー、または Active Bar を使用して配置します。

カバーを BOM のコンポーネントとして扱う

Layout Drawing 内のハーネスカバーが BOM 内のコンポーネントとして扱われるようになり、part choices とグループ化を対応します。

追加の物理ビューのコンポーネント プロパティを表示

ハーネスコンポーネントの追加の物理ビューがデザインスペースで選択されると、メイン (最初の) 物理ビューの場合と同様に、Properties パネルにコンポーネント自体のプロパティが表示されるようになりました。下図では、デザインスペースで 2 番目の物理ビューが選択されています; Harness Component Properties パネルには、元の (最初の) 物理ビューのプロパティが表示されます。

Wiring List の改善

Wiring List を '分割' する機能を追加

高度なハーネスデザインの wiring list には多数のエントリが含まれる場合があり、単一の表として図面ドキュメントに収めるのが困難な場合があります。フォントや表のスケーリング、複数のカスタム表エントリ、または外部ドキュメントに頼るのではなく、Harness Draftsman ドキュメント内の Wiring List を '分割' して、Wiring List を複数の 'ページ' にまたがって表示できるようになりました。この新しい機能を使用するには、配置された Wiring List の Properties パネルで、Pages 領域の Limit Page Height オプションを有効にします。これにより、Wiring List 表の高さが指定された高さ (Max Page Height) に制限され、従って、表に表示される行数が制限されます。

| ❯❮ |

エディタは、パネルの Page エントリ (例えば、1 から 2) で示されるように、Wiring List 全体が表示されていないことを検出し、関連するドロップダウン メニューを使用して、どのページを表示するかを指定できます。Wiring List のページを更に追加するには、別の Wiring List (Place » Wiring List) を配置し、Properties パネルの Pages 領域で次の Page を指定します。

'接続付きシールド' オブジェクトのための強化された Wiring List

ワイヤがシールドのコネクタへ接続されている時、コネクタオブジェクト付きシールドのデジグネータが Wiring List に表示されるようになりました。

スプライスの接続テーブルを表示する機能を追加

個々のスプライスの接続テーブルを表示する機能を追加しました。以前は、コンポーネントとコネクタのみの接続テーブルを表示できました。

クロスプローブ用にテキストフレームと注釈オブジェクトへ追加されたリンク

オブジェクト デジグネータをテキストフレームや注釈にアクティブリンクとして追加できるようになりました。リンクは、Wiring Diagram と Layout Drawing でクロスプローブ機能として働きます。アクティブリンクを作成するには、Wiring Diagram、または Layout Drawing にテキストフレーム、または注釈オブジェクトを配置します。Properties パネルの Properties 領域の Text 欄に "@" と入力します。全てのデジグネータのドロップダウンが表示されます。リストから目的のデジグネータをダブルクリックします。リンクは Text 欄とデザインスペースに作成されます。デザインスペース内のリンクをクリックして、関連するドキュメント (つまり、現在、アクティブではないドキュメント) 内のそのオブジェクトへクロスプローブできます。このプロセスは、以下のビデオで説明されています。

データ管理の改善

Manufacturer Lifecycle State メッセージの強化

SiliconExpert 統合機能を使用すると、メーカーの部品のライフサイクルデータを様々なソース (Altium Parts Provider (Octopart、または IHS Markit® を利用) や SiliconExpert) から取得できます。様々なソースからのこのライフサイクルデータをよりわかりやすく表示するために、利用可能な全てのソースからのライフサイクル情報にアクセスできるようになりました。

manufacturer part データ (Manufacturer Part Search パネル のエントリ、Workspace ライブラリ コンポーネントの part choice、AcitveBOM ドキュメント のソリューション等) を調べる時、manufacturer lifecycle state/bar の上にカーソルを置くか、ドロップダウンを使用すると、ツールチップ内の全てのソースからのライフサイクル情報を表示できます。

| ❯❮ |

オフライン Workspace プロジェクトの Project Options へ General タブを追加

オフライン Workspace プロジェクトの Project Options ダイアログへ General タブを追加しました。この機能は、Workspace から切断されている時にプロジェクトで作業するために利用できます。このタブ上でアクセスできる唯一のコントロールは、Turn Off Synchronization ボタンです。同期をオフにするには、このボタンをクリックします。これにより、ローカルコピーが Workspace 上にあるコピーにリンクされなくなります。Workspace にあるプロジェクトはそのまま残ります。

Removed Commit Command for Git-based Projects

Git ベースのプロジェクトの場合、データがコミットされる (リモートリポジトリではなくローカルリポジトリに対して) 場所に関する混乱を避けるために、Projects パネルのプロジェクトエントリの右クリックメニューと Project メインメニューの History & Version Control サブメニューから Commit コマンドを削除しました。コマンドの表示は、Advanced Settings ダイアログ の VCS.AllowGitCommit オプションでコントロールします (デフォルトではオフ)。Save to Server コマンドを使用すると、1 回の操作でプロジェクトをローカルリポジトリへコミットし、リモートリポジトリへ反映できます。

インポート/エクスポートの改善

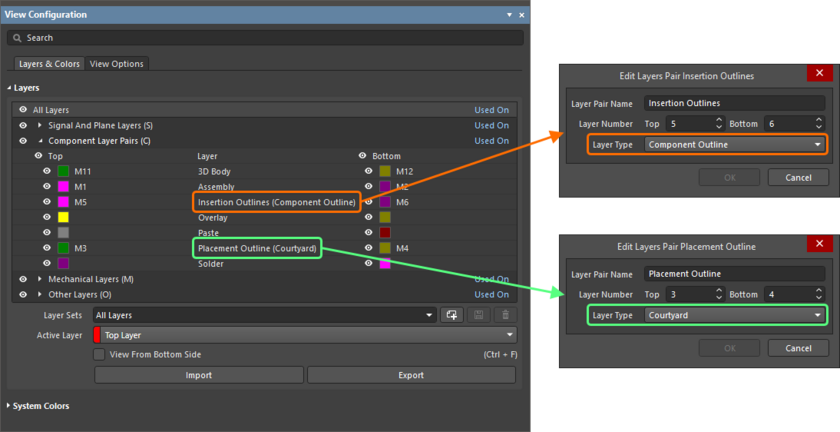

Mentor Xpedition Placement Outline と Insertion Ouline Layer のマッピング

Mentor Xpedition PCB とフットプリント ライブラリ ファイルがインポートされる時、Placement Outline layer type が Courtyard layer type としてマッピングされ、Insertion Outline layer が Altium Designer の Component Outline layer type へマッピングされるようになりました。

回路シミュレーションの改善

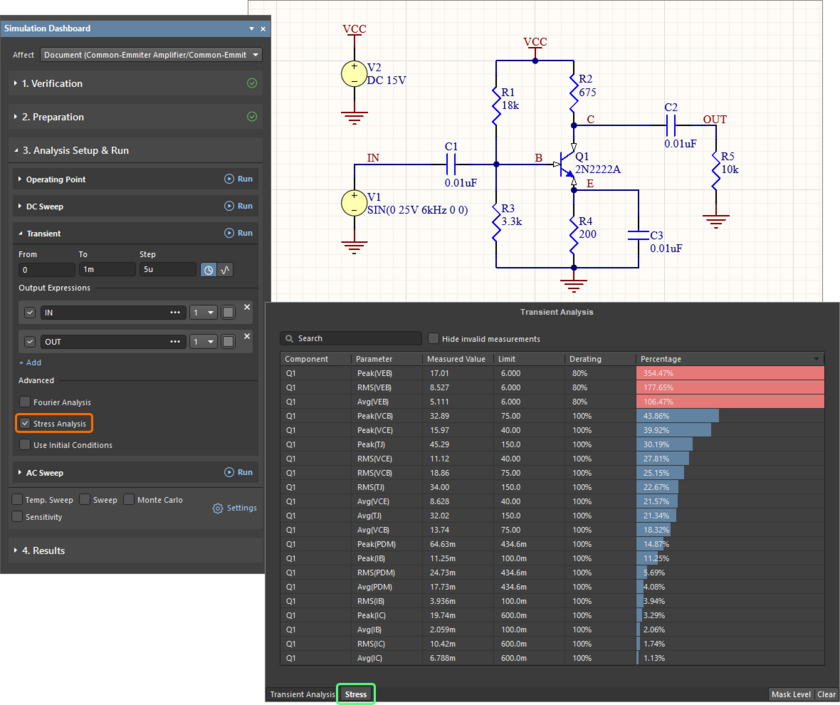

シミュレーション Stress Analysis (応力解析) (Open Beta)

Stress Analysis は、最大電圧、電流、消費電力などの個々のコンポーネントの動作条件を計算し、コンポーネントの stress モデルで定義された制限と照らし合わせてチェックするために使用します。

このバージョンでは、新しい Stress Analysis オプションを Simulation Dashboard の Transient 領域へ追加しました。このオプションが有効で過渡解析が実行されると、simulation result ドキュメントの追加の Stress チャートで Stress analysis の結果を確認できます。

新しい Stress Analysis を使用して、定義された制限に対して回路をテストできます。

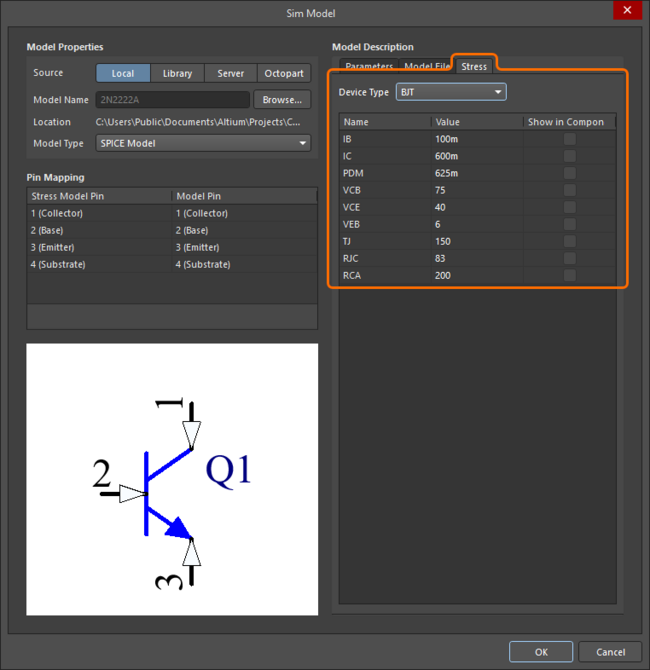

コンポーネントの stress モデルは、Sim Model ダイアログ (コンポーネントのシミュレーションモデルにアクセスする) の新しい Stress タブで設定します。ここから、必要な Device Type を選択し、パラメータ値を定義できます。

コンポーネントの Stress analysis パラメータは、Sim Model ダイアログの Stress タブで設定できます。

Altium Designer 24.1 で完全に公開された機能

以下の機能は、このバージョンで正式に公開されました:

- Custom Paste/Solder Masks – 23.8 から利用可能

Altium Designer 24.0

リリース日: 2023年12月13日 – バージョン 24.0.1 (build 36)

Altium Designer バージョン 24.0.1 のリリースノート

PCB デザインの改善

Any Angle Diff Pair Router (Open Beta)

このバージョンでは、任意の角度の差動ペア配線を対応しました。Interactive Differential Pair Routing ツール (Route » Interactive Differential Pair Routing) を使用して差動ペアを配線する場合、Differential Pair Routing モードの Properties パネルで配線のプロパティを設定する時に、Any Angle コーナースタイル (![]() ) を選択できるようになりました。

) を選択できるようになりました。

- 任意の角度の差動ペア配線では、対称的なパッドへの配線とギャップ変更を対応します。

- アンテナから差動ペア配線を開始する場合、ネットの左から右の順番を維持し (つまり、左側の続きは左側に残ります)、元の方向へのスナップを対応します。

- Any Angle コーナースタイルを使用して差動ペアを配線する時、Shift キーを押したままにして、接線円弧を使用して差動ペアを配線できます。

任意の角度の差動ペア配線のデモンストレーション。

この機能は、Route » Gloss Selected コマンドを使用する時、更新された角度の差動ペアの glossing アルゴリズムも有効になることに注意してください。

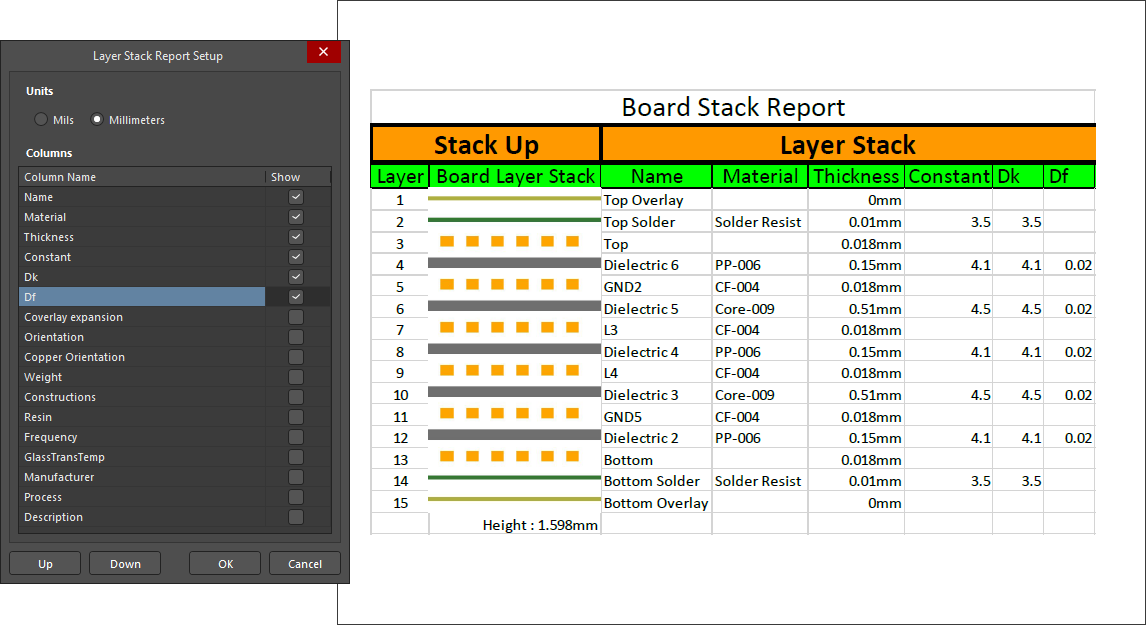

Layer Stack Report Setup ダイアログの強化 (Open Beta)

Layer Stack Report Setup ダイアログ (File » Fabrication Outputs » Report Board Stack) を強化し、レイヤ構成に存在する全ての列が含まれるようになりました。ダイアログを使用して、Layer Stack Report に表示したい列を選択できます。

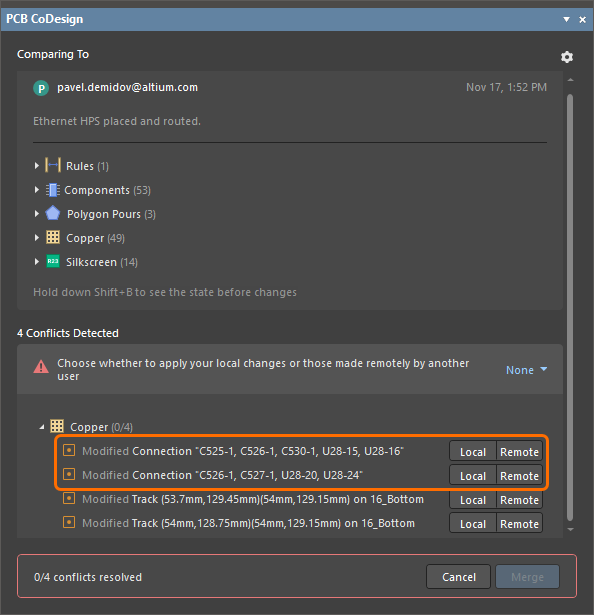

PCB CoDesign の改善

銅箔の不一致の表示と解決の強化

銅箔オブジェクトの不一致は、変更の調査と解決を容易にするために、該当する場合にはピン間接続グループにグループ化されるようになりました。

銅箔の不一致をピン間接続レベルで解決できるようになりました。

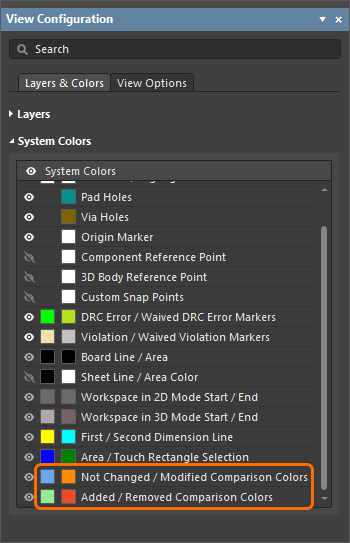

色を設定する機能の追加

View Configuration パネル で、追加、変更、削除されたオブジェクト、および変更されていないオブジェクト (PCB CoDesign パネルで選択されている場合は、ピン間接続の変更されていないオブジェクト) の色を選択できるようになりました。

View Configuration パネルを使用して、比較色を設定できます。

その他の PCB CoDesign UI の変更

- 比較の実行直後に、比較が進行中であることを示すポップアップが表示されるようになりました。

- 変更リスト内のエントリを選択、および選択解除する機能を追加しました。エントリが選択されている時 (クリックして)、再度、クリックするとエントリの選択が解除され、デザインスペース内のオブジェクトのハイライト表示がリセットされます。

- PCB CoDesign パネルを使用して変更を統合した後に表示される Project パネルの Merged アイコン (

) のメニューへ Save to Server コマンドを追加しました – 画像を表示。

) のメニューへ Save to Server コマンドを追加しました – 画像を表示。 - 変更を統合した後、PCB CoDesigner パネルで Save to Server ボタンをクリックすると、デフォルトで、統合された PCB ドキュメントのみが Save to Server ダイアログで選択されます – 画像を表示。

- 変更の統合を実行すると、統合が進行中であることを示す新しいポップアップが表示されます – 画像を表示。

制約マネージャの改善

差動ペアクラスを Clearance Matrix へ追加する機能

このバージョンから、ネットクラスだけでなく、差動ペアクラスも Clearance Matrix (Clearances 画面) へ追加できます。

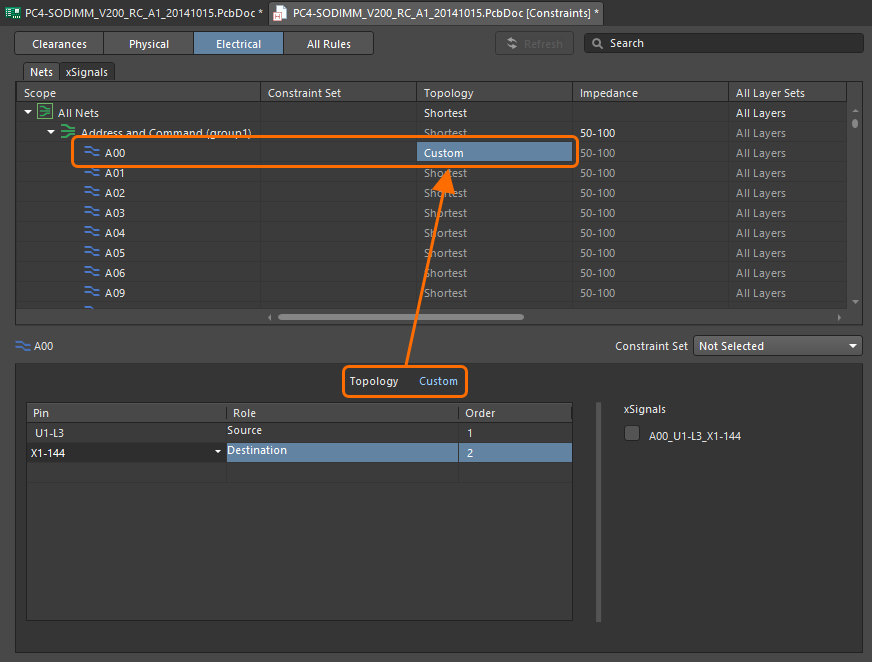

PCB 側でのカスタム トポロジの編集

ネットのトポロジを Custom として定義し、PCB 側からアクセスする時に 制約マネージャ で必要に応じて、編集できるようになりました。

Constraint Set 編集時のトポロジ変更の反映

カスタム トポロジを含む Constraint Set を編集する場合、トポロジへの変更は、この Constraint Set が適用される他のオブジェクトへ反映されるようになりました。

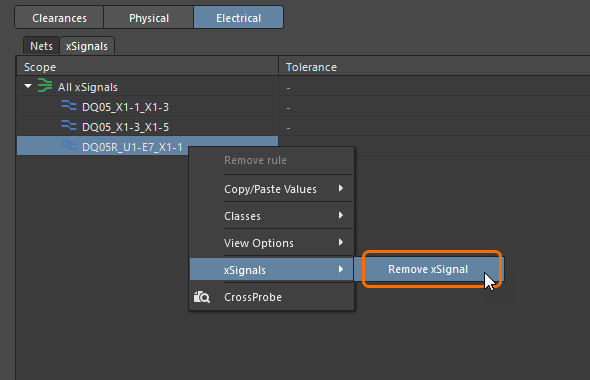

Xsignals を削除する機能

Electrical 画面の xSignals タブから xSignal を削除できるようになりました。これを行うには、xSignal を右クリックし、メニューから xSignals » Remove xSignal コマンドを選択します。

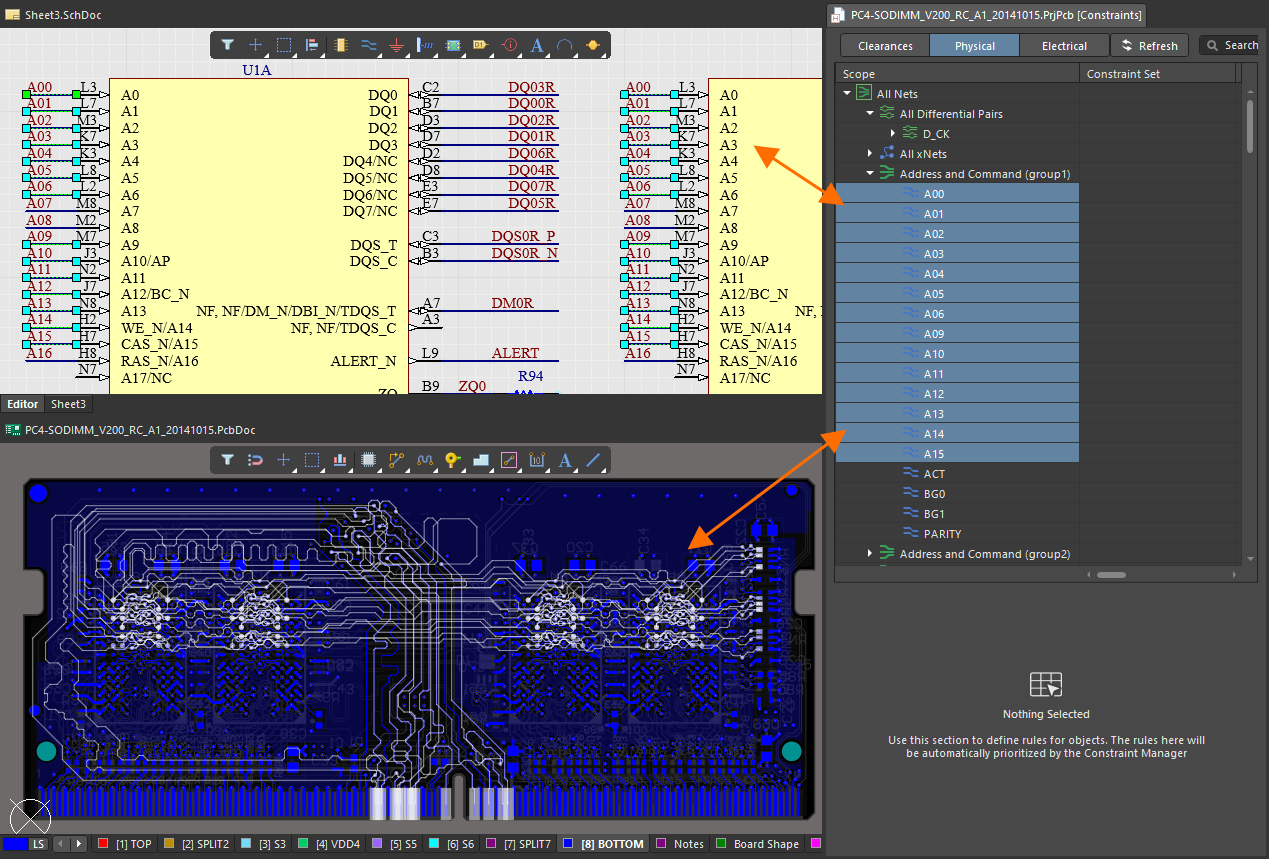

制約マネージャとの間の相互選択

このバージョンでは、制約マネージャとの間でオブジェクトを相互選択する機能を追加しました。クロスセレクト モードが有効になっている場合 (回路図エディタ、または PCB エディタでの 制約マネージャ の Tools メインメニューから Cross Select Mode コマンドを使用して)、制約マネージャ で選択したオブジェクトは、回路図ドキュメントと PCB ドキュメントでも選択されます。その逆も同様です。

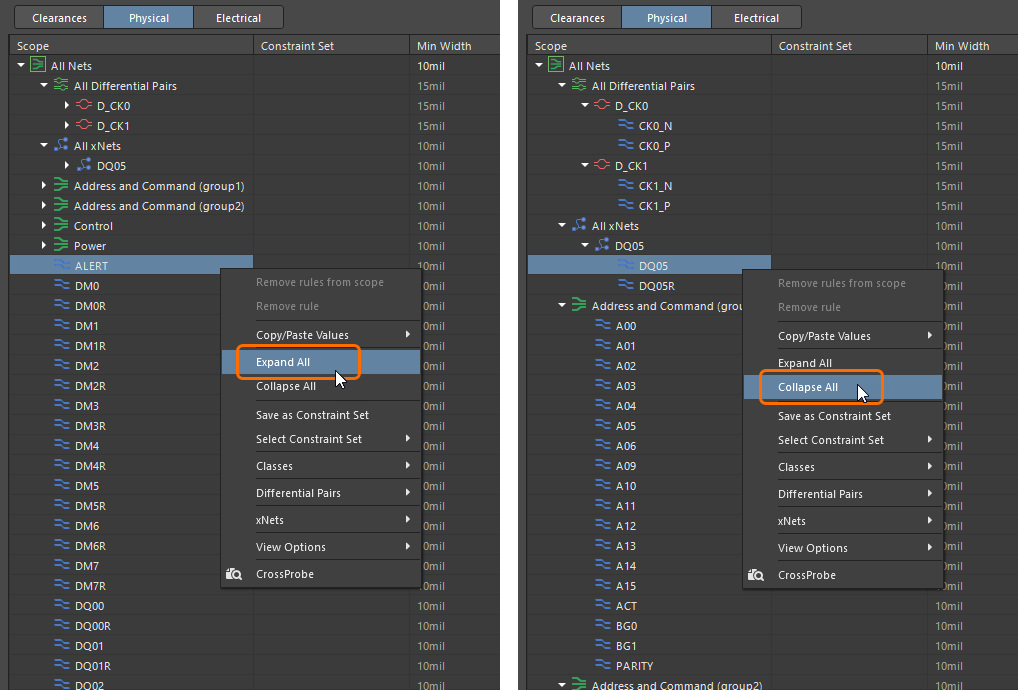

展開/折りたたみ状態の強化

事前定義されたノード (例: All Nets) を除く全てのノードは、デフォルトで Physical と Electrical 画面で折りたたまれます。新しい Expand All と Collapse All 右クリックメニューコマンドを使用して、リストをコントロールできます。

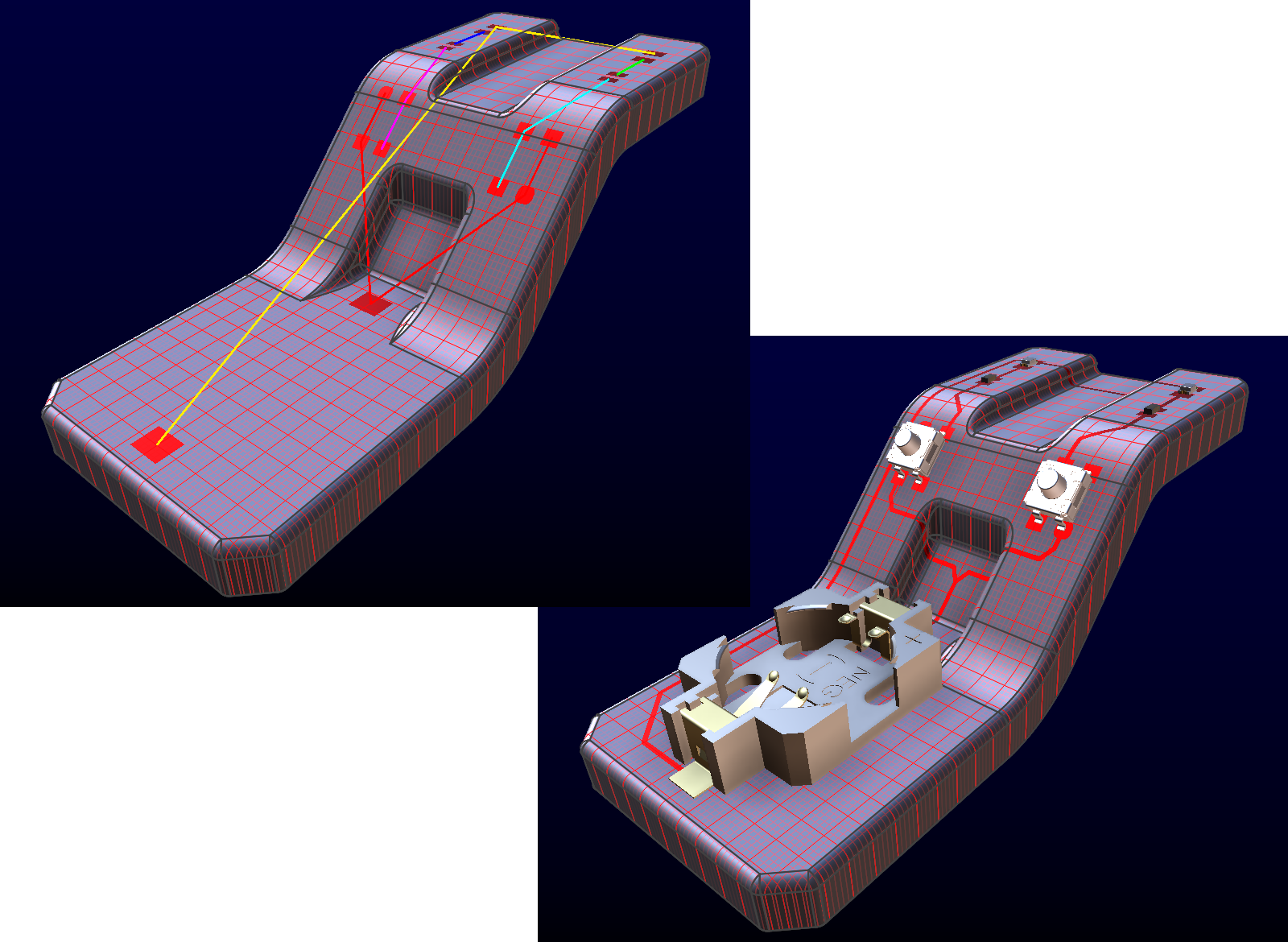

3D-MID デザイン (Open Beta)

3D-MID テクノロジーは、電気回路と 3 次元の機構部品を結合させます。この機能の融合により、広範囲のアプリケーション分野で可能性の世界が開きます。

これまで、適切な ECAD ツールが無かったため、3D-MID の設計者は一般に MCAD パッケージに限定されてきました。この作業方法には多くの問題があり、特に、回路レイアウトを駆動するための電気的機能が欠如していることと、2D の手動で描かれたスケッチを 3D 表面に投影することに伴う困難さが挙げられます。

Altium Designer の新しい 3D-MID エディタを使用すると、標準の表面実装コンポーネントを 3D-MID ドキュメント内の 3D 形状に配置し、形状の表面に沿って配線してレイアウトを完成させることができます。

完成したデザインは、Laser Direct Structuring (LDS) 製造プロセスに必要なファイル形式でエクスポートできます。

ハーネスデザインの改善

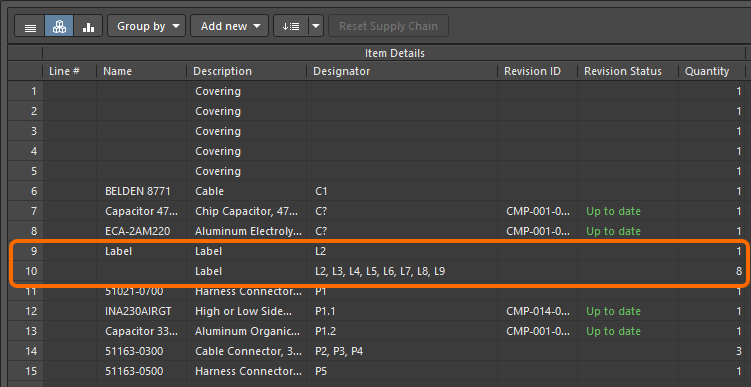

レイアウトラベルを BOM のコンポーネントとして扱う

Layout Drawing (レイアウト図) 内のレイアウトラベルが BOM 内のコンポーネントとして扱われるようになり、part choices とグループ化を対応するようになりました。

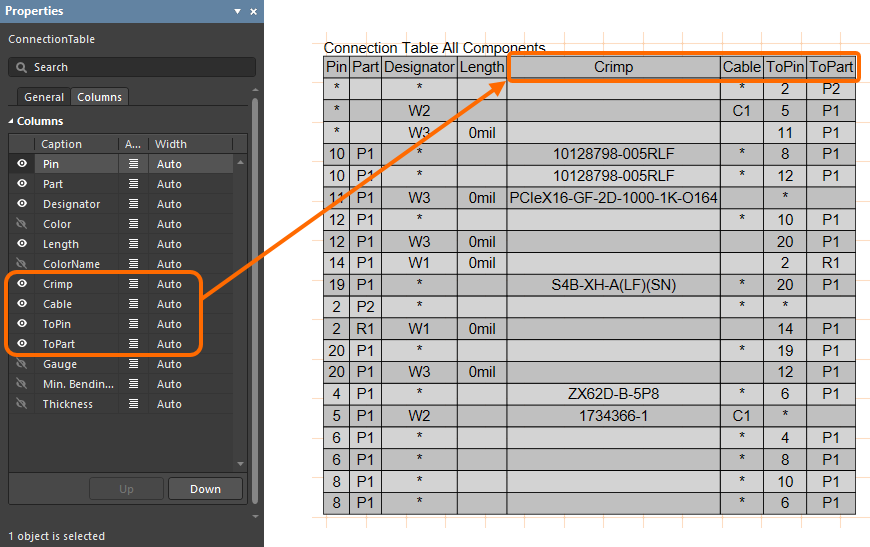

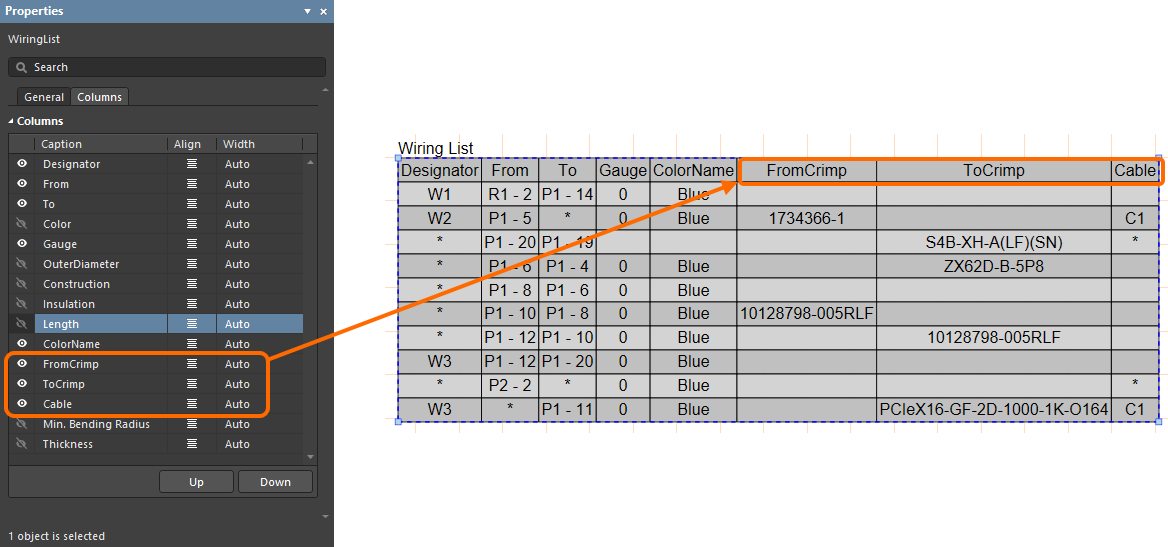

Connection Table と Wiring List へ列を追加

Manufacturing Drawing (*.HarDwf) の Connection Table と Wiring List に列を追加し、デザインスペースで追加情報を簡単に表示できます。Crimp (圧着) (part number)、Cable、ToPin、ToPart を Connection Table へ追加しました。FromCrimp、ToCrimp、Cable を Wiring List へ追加しました。Properties パネルにある目のアイコンを切り替えて、Connection Table 内の目的の列を表示/非表示できます。

プラットフォームの改善

長いパス名の対応 (Open Beta)

このバージョンでは、長いパス名を対応しました。ファイル名を含むファイルパスが 256 文字を超える場合、以下の様なファイルに対する動作を対応するようになりました:

- 接続された Workspcae からプロジェクトを開く。

- ローカルプロジェクトを Workspace で使用できるようにする。

- 出力ジョブファイル内のフォルダパスを変更する。

- 出力ジョブファイル、または Project Releaser を使用して出力を生成する。

- プロジェクトをプロジェクトテンプレートとして Workspace へ保存する。

Windows 10 バージョン 1607 以降、一般的な Win32 ファイル、およびディレクトリ関数から MAX_PATH の制限が削除されました。ただし、Altium Designer がインストールされているコンピュータのレジストリ キーを変更して、新しい動作をオプトインする必要があります。詳細については、Support for Long Path Names のページをご参照ください。その後、コンピュータが再起動されていることを確認してください。

インポート/エクスポートの改善

xDX Designer のインポートの改善

このバージョンでは、xDX Designer デザインファイルの Altium Designer へのインポートに関連する多くの重要な改善と修正が行われています。

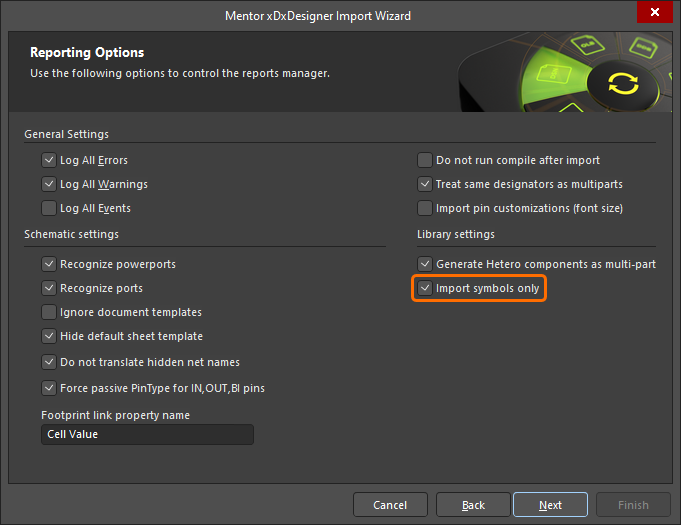

シンボルのみをインポートする機能を追加

Mentor xDxDesigner Import Wizard の Reporting Options ページに、シンボルのみをインポートできる Import symbols only オプションを含めました。このオプションを有効にすると、元のライブラリの多くのコンポーネントが使用されている場合でも、ライブラリ データベースからの同一のシンボルが 1 つの回路図シンボルとしてインポートされ、パラメータは Altium Designer のシンボルへインポートされません。

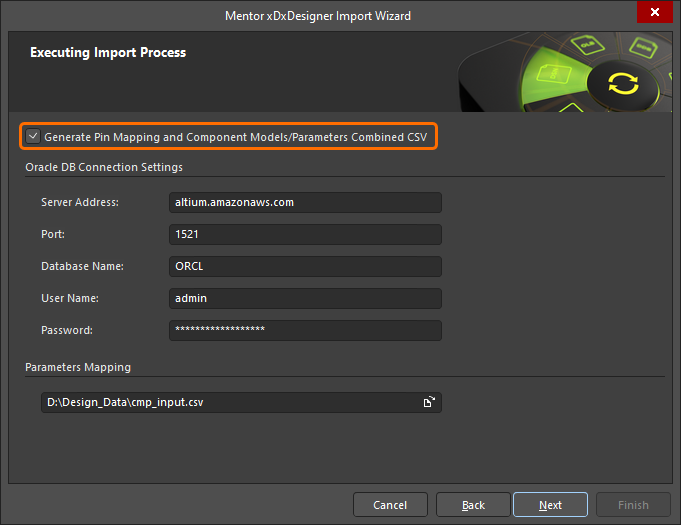

また、このオプションが有効になっている場合、ウィザードの次のページでは、Generate Pin Mapping and Component Models/Parameters Combined CSV オプションを有効にして、部品シンボルとピンマッピング データを CSV 形式で生成するように設定できます。このオプションが有効な場合、使用可能な欄を使用して、Oracle DB 接続パラメータとパラメータ マッピング ファイルを定義できます。

マルチパート シンボルのインポートの改善

Altium Designer へインポートされると、マルチパート シンボルは、xDX Designer で定義された最初と最後のパート名と組み合わせられた Design Item ID を受け取ります。これらの結合された Design Item ID は、生成される CSV ファイルでも使用されます。

また、Altium Designer へインポートされたシンボル内のパートの順番は、元のライブラリで定義されたものと同じになりました。

シンボルのインポートの改善

その他のインポートの改善点は、以下の通りです:

- シンボル内の静的テキストがインポートされるようになりました。

- xDX Designer で負論理に使用される '

~' 文字は、Altium Designer で負論理記号を正しく表すために、ピン名の '\' 文字に変換されるようになりました。 -

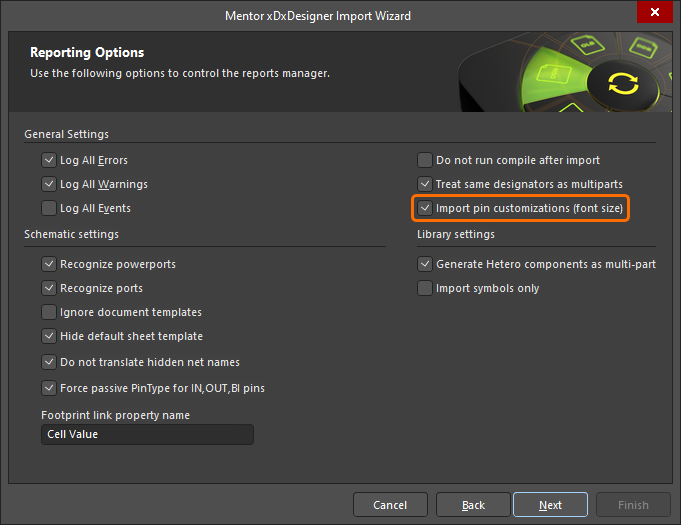

Mentor xDxDesigner Import Wizard の Reporting Options ページに、Import pin customizations (font size) オプションを含めました。このオプションを有効にすると、pin designator と name が xDX Designer と同じフォントサイズで Altium Designer へインポートされます。

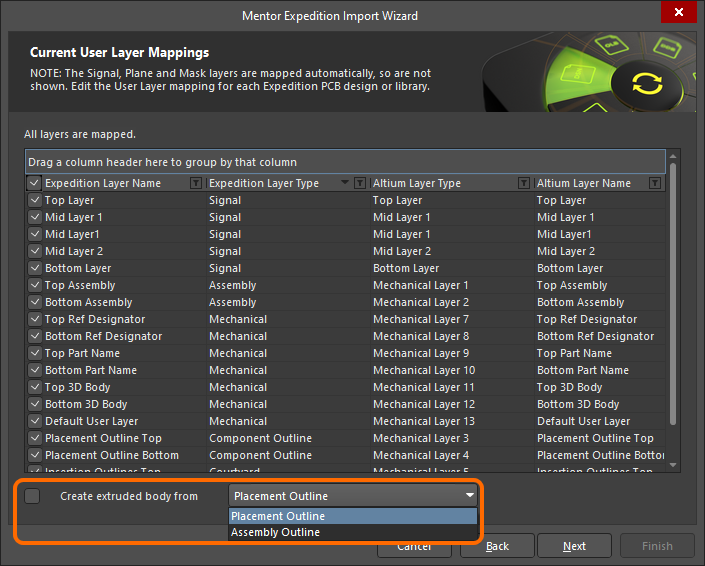

Mentor Expedition インポートの改善

Extruded Body Layer を選択する機能を追加

インポート ウィザード を使用して Mentor Expedition ファイルをインポートする場合、extruded body を作成するレイヤを選択できるようになりました。インポートする Mentor PCB ファイルとライブラリファイルを追加した後、Current User Layer Mappings ページの Create extruded body from ドロップダウンを使用して、Placement Outline、または Assembly Outline から選択します。このオプションが有効な場合、デフォルトは Placement Outline です。

Placement Outline の改善

Placement Outline を、Top/Bottom 3D Body assembly layer 上の Placement Outline layer にプリミティブとしてインポートできるようになりました。

回路シミュレーションの改善

P-Channel トランジスタの出力電流を反転

P-Channel トランジスタ (BJT、JFET、MOSFET、MESFET) の出力電流は流入電流として扱われるようになり、N-Channel トランジスタと一致するようになりました。

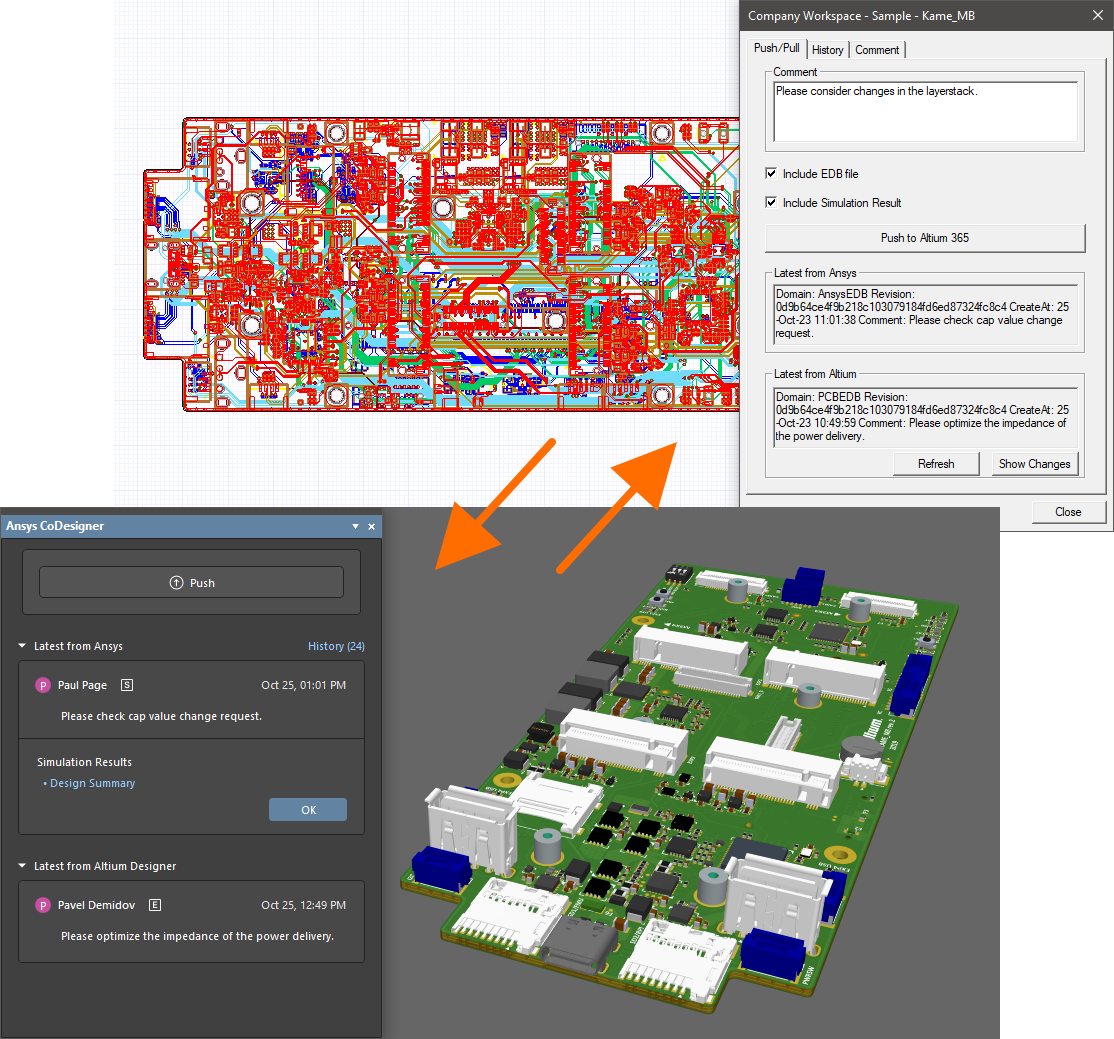

Ansys CoDesigner (Open Beta)

このバージョンは、ECAD とシミュレーション領域間の真の共同作業設計 (CoDesign) への最初のステップを示します。これまで、これら 2 つの孤立化された陣営の技術者は、設計の改訂とは関係のない手動によるファイルのエクスポート/インポート プロセスに依存し、設計領域外での変更と結果の伝達 (通常は Eメール) に頼らなければなりませんでした。

Ansys CoDesigner 機能の登場により、ECAD 技術者 (Altium Designer を使用) は、同僚の SIM 技術者 (Ansys Electronics Desktop (AEDT) を使用) とシームレスに設計で共同作業できるようになりました。共同作業は、2 つの領域間の橋渡しとして機能する Altium 365 Workspace を通じて容易になります。この初期バージョンには、以下の主要な要素の対応が含まれています:

- 2 つの領域間の設計変更の双方向の push/pull。Altium Designer から、レイヤ構成、材料、コンポーネント、プリミティブへの変更が検出され、AEDT に適用できます。AEDT から、レイヤ構成と材料へ提案された変更を EDB ファイルを通じて push し、Altium Designer で検出/適用できます。

- シミュレーション結果は AEDT から Altium 365 Workspace へ push され、デザインのレビジョンに関連付けられ、Workspace のブラウザインターフェースを通じて表示したり、Altium Designer 内でプレビューできます。

- コメント システムを使用した双方向通信。各コメント スレッドはデザイン内の特定のコンポーネントへ関連付けられます。

Keysight のパワーアナライザーの改善

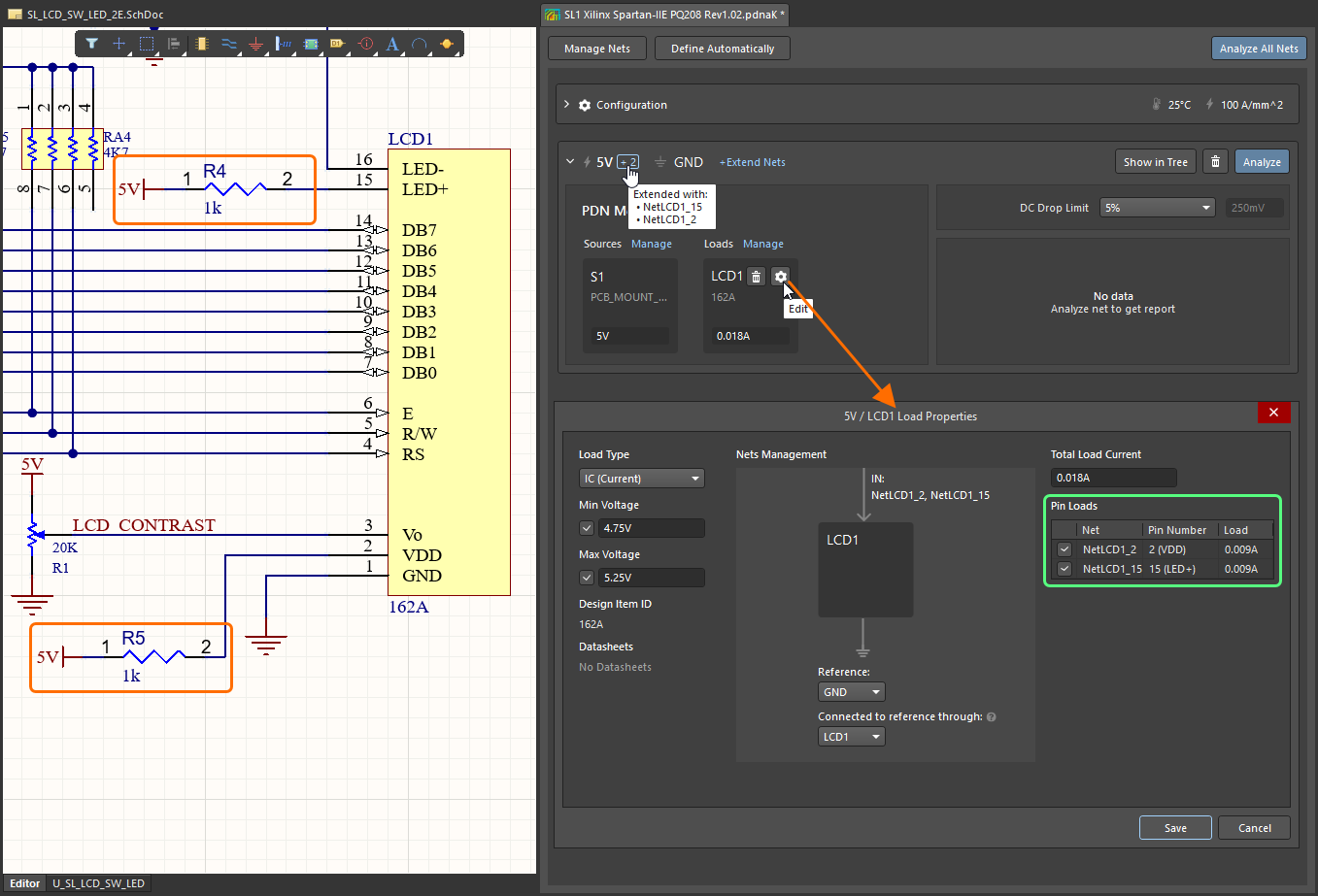

同じコンポーネント上の複数のネットに電流を割り当てる機能を追加

このバージョンでは、異なる直列要素の同じコンポーネント上の複数のネットに電流を割り当てる機能を追加しました。

IC (電流) タイプの負荷を設定する場合、様々なシリアル コンポーネントを介してソースに接続する負荷コンポーネントの全てのピンを確認でき、必要なピンを選択できます。

以下に示す例では、5V 電源ネットが R4 と R5 シリーズ コンポーネントを介して LCD1 コンポーネントの 2 つのピンに接続されています。電源ネットを拡張し、LCD1 を負荷として追加した後、Load Properties ダイアログで必要に応じて、両方のピンを選択して設定できます。

ALTIUM DESIGNER 24.0で完全に公開された機能

以下の機能は、このバージョンで正式に公開されるようになりました:

- Constraint Manager - 23.11 から利用可能

- PCB CoDesign - 23.10 から利用可能

- Harness Design - 23.0 から利用可能

- Improved Detection of Minimum Annular Ring Violation - 22.10 から利用可能